Important Concepts

:- What are flip flops, registers and latches? how do we avoid latches?

- What are what are counters and shift registers?

- How to make a register or a wire with a signal and VHDL?

- What is debouncing? How to use buttons on FPGA board and mitigate debouncing?

Exercise Questions

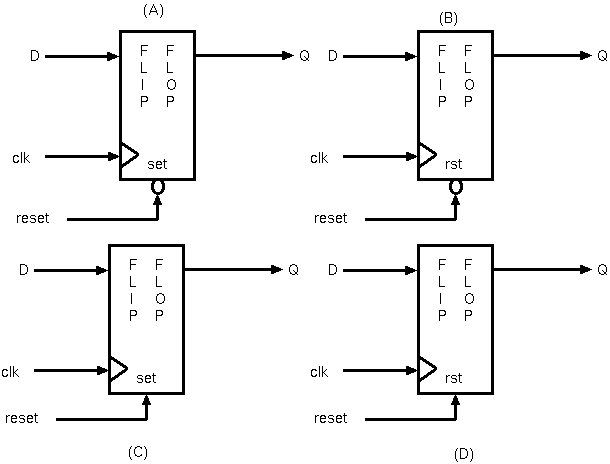

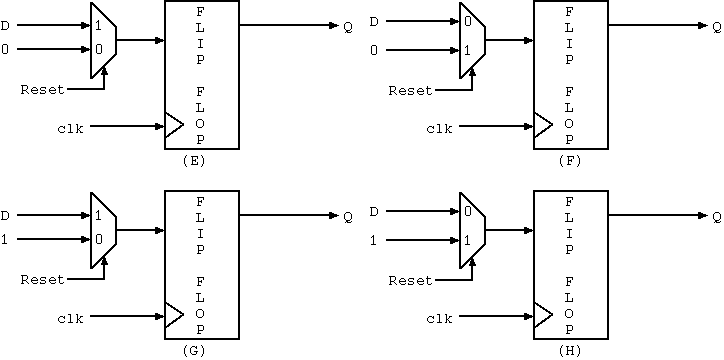

- Fill the correct diagrams and Codes in the table

| Diagram | Code | |

| Dflipflop with asynchronous negetive Reset to 1 | Figure(_________) | Code(_________) |

| Dflipflop with asynchronous negetive Reset to 0 | Figure(_________) | Code(_________) |

| Dflipflop with asynchronous postive Reset to 1 | Figure(_________) | Code(_________) |

| Dflipflop with asynchronous postive Reset to 0 | Figure(_________) | Code(_________) |

| Dflipflop with synchronous negetive Reset to 0 | Figure(_________) | Code(_________) |

| Dflipflop with synchronous positive Reset to 0 | Figure(_________) | Code(_________) |

| Dflipflop with synchronous negetive Reset to 0 | Figure(_________) | Code(_________) |

| Dflipflop with synchronous positive Reset to 0 | Figure(_________) | Code(_________) |

- Code(1)

signal d,clk,q,reset :std_logic; process(clk,d) begin if (clk’event and clk=’1’) then if reset = '1' then q <= '0'; else q <= d; end if; end if; end process;

- Code (2)

signal d,clk,q,reset :std_logic; process(clk,d) begin if (clk’event and clk=’1’) then if reset = '1' then q <= '1'; else q <= d; end if; end if; end process;

- Code (3)

signal d,clk,q,reset :std_logic; process(clk,d) begin if (clk’event and clk=’1’) then if reset = '0' then q <= '0'; else q <= d; end if; end if; end process;

- Code (4)

signal d,clk,q,reset :std_logic; process(clk,d) begin if (clk’event and clk=’1’) then if reset = '0' then q <= '1'; else q <= d; end if; end if; end process;

- Code (5)

signal d,clk,q,reset :std_logic; process(clk,d) begin if reset = '1' then q <= '0'; elsif (clk’event and clk=’1’) then q <= d; end if; end process;

- Code (6)

signal d,clk,q,reset :std_logic; process(clk,d) begin if reset = '1' then q <='1'; elsif (clk’event and clk=’1’) then q <= d; end if; end process;

- Code (7)

signal d,clk,q,reset :std_logic; process(clk,d) begin if reset = '0' then q <='0'; elsif (clk’event and clk=’1’) then q <= d; end if; end process;

- Code (8)

signal d,clk,q,reset :std_logic; process(clk,d) begin if reset = '0' then q <= '1'; elsif (clk’event and clk=’1’) then q <= d; end if; end process;

| ### | REGISTER WITH COMBINATIONAL CIRCUIT | LATCH WITH COMBINATIONAL CIRCUIT | ONLY COMBINATIONAL CIRCUIT | Description of the resulting design |

| Code 1 | yes(_____)/No(_____) | yes(_____)/No(_____) | yes(_____)/No(_____) | |

| Code 2 | yes(_____)/No(_____) | yes(_____)/No(_____) | yes(_____)/No(_____) | |

| Code 3 | yes(_____)/No(_____) | yes(_____)/No(_____) | yes(_____)/No(_____) | |

| Code 4 | yes(_____)/No(_____) | yes(_____)/No(_____) | yes(_____)/No(_____) | |

| Code 5 | yes(_____)/No(_____) | yes(_____)/No(_____) | yes(_____)/No(_____) | |

| Code 6 | yes(_____)/No(_____) | yes(_____)/No(_____) | yes(_____)/No(_____) |

- Code 1

signal c,a,b,select,clk :std_logic; process(clk,a,b,select) begin if (clk’event and clk=’1’) then if select = '1' then c <= a and b; else c <= a or b; end if; end if; end process;

- Code 2

signal c,a,b,select,clk :std_logic; process(clk,a,b,select) begin if (clk’event and clk=’1’) then if select = '1' then c <= a and b; end if; end if; end process;

- Code 3

signal c,a,b,select :std_logic; process(a,b,select) begin if select = '1' then c <= a and b; end if; end process;

- Code 4

signal c,a,b,clk :std_logic; process(clk,a,b) begin if (clk=’1’) then c <= a and b; end if; end process;

- Code 5

signal c,a,b,clk :std_logic; process(clk,a,b) begin c <= a or b; if (clk=’1’) then c <= a and b; end if; end process;

- Code 6

signal c,a,b,clk :std_logic; process(clk,a,b) begin if (clk=’1’) then c <= a and b; else c <= a or b; end if; end process;

| -- | Shift Register | Description the design |

| Code 1 | yes(_____)/No(_____) | - |

| Code 2 | yes(_____)/No(_____) | - |

| Code 3 | yes(_____)/No(_____) | - |

| Code 4 | yes(_____)/No(_____) | - |

- Code 1

signal s0,s1,s2,s3,clk :std_logic; process(clk,s1,s2,s0) begin if (clk’event and clk=’1’) then s1 <= s0; s2 <= s1; s3 <= s2; end if; end process;

- Code 2

signal clk :std_logic; process(clk,s1,s2,s0) variable s0,s1,s2,s3 :std_logic; begin if (clk’event and clk=’1’) then s1 := s0; s2 := s1; s3 := s2; end if; end process;

- Code 3

signal clk :std_logic; process(clk,s1,s2,s0) variable s0,s1,s2,s3 :std_logic; begin if (clk’event and clk=’1’) then s3 := s2; s2 := s1; s1 := s0; end if; end process;

- Code 4

signal s0,s1,s2,s3 :std_logic; process(S0,s1,s2) begin s1 <= s0; s2 <= s1; s3 <= s2; end process;