Difference between revisions of "CPUProject"

From ATI public wiki

m |

m |

||

| Line 133: | Line 133: | ||

== Control unit== | == Control unit== | ||

| + | [[File:ControllerFSM.png|400px|thumb|right]]] | ||

| + | [[File:InstDec.png|400px|thumb|right]] | ||

== Instruction Memory (ROM) == | == Instruction Memory (ROM) == | ||

== Data Memory == | == Data Memory == | ||

Revision as of 11:00, 5 December 2014

CPU project is one of the projects designed in department of computer engineering at TTU as a lab project. The main aims of this project are:

- Developing a generic CPU without any fancy feature

- Writing a compiler for it

- Compiling GCC for this architecture

- Booting a light linux on it

Contents

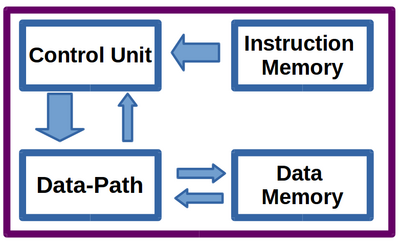

CPU Design

Functionality Requirements

The CPU is supposed to be able to perform the following operations:

- Addition/Subtraction

- Increment/Decrement

- Arithmetic and Logical Shift

- Bitwise AND, OR, XOR and NOT

- Negation

- Load/Store

- Unconditional Branch (jump)

- Branch if zero / Branch if Overflow / Branch if Carry

- Clear Registers/Flags

- PUSH / POP

- NOP/HALT

Architecture

Instruction Format

Our CPU's instuction has 8 bit of upcode and one operand that can be as long as 32 bit. First 2 bits of OPcode are at the moment reserved.

Instruction Set (IS)

The following instrcutions designed for the CPU:

| Instruction | Register Transfer Language | OpCode | DPU Command | Data To DPU | MemAddress | Next PC | |

|---|---|---|---|---|---|---|---|

| 1 | Add_A_B | A <-- A + B | XX00 0000 | 00 000 0000 10 | ---- | ---- | PC_out+1 |

| 2 | Add_A_Mem | A <-- A + Mem[Operand] | XX00 0001 | 00 000 0000 00 | ---- | Operand | PC_out+1 |

| 3 | Add_A_Dir | A <-- A + Operand | XX00 0010 | 00 000 0000 01 | Operand | ---- | PC_out+1 |

| 4 | Sub_A_B | A <-- A - B | XX00 0011 | 00 000 0001 10 | ---- | ---- | Example |

| 5 | Sub_A_Mem | A <-- A - Mem[Operand] | Example | 00 000 0001 00 | ---- | Operand | PC_out+1 |

| 6 | Sub_A_Dir | A <-- A - Operand | Example | 00 000 0001 01 | Operand | ---- | PC_out+1 |

| 7 | IncA | A <-- A + 1 | Example | 00 000 0000 11 | ---- | ---- | PC_out+1 |

| 8 | DecA | A <-- A - 1 | Example | 00 000 0001 11 | ---- | ---- | PC_out+1 |

| 9 | ShiftArithR | A <-- A(7) & A(7 downto 1) | Example | 00 000 0111 00 | ---- | ---- | PC_out+1 |

| 10 | ShiftArithL | A <-- A(7) & A(5 downto 0)& '0' | Example | 00 000 1000 00 | ---- | ---- | PC_out+1 |

| 11 | ShiftA_R | A <-- A(6 downto 0)& '0' | Example | 00 000 1010 00 | ---- | ---- | PC_out+1 |

| 12 | ShiftA_L | A <-- '0' & A(7 downto 1) | Example | 00 000 1011 00 | ---- | ---- | PC_out+1 |

| 13 | RRC | A <-- C & A(7 downto 1) ,C<-- A(0) | Example | 00 000 1110 XX | ---- | ---- | PC_out+1 |

| 14 | RLC | A <-- A(6 downto 0) & C ,C<-- A(7) | Example | 00 000 1111 XX | ---- | ---- | PC_out+1 |

| 15 | And_A_B | A <-- A and B | Example | 00 000 0100 10 | ---- | ---- | PC_out+1 |

| 16 | OR_A_B | A <-- A or B | Example | 00 000 0101 10 | ---- | ---- | PC_out+1 |

| 17 | XOR_A_B | A <-- A xor B | Example | 00 000 0110 10 | ---- | ---- | PC_out+1 |

| 18 | FlipA | A <-- not (A) | Example | 00 000 1100 00 | ---- | ---- | PC_out+1 |

| 19 | NegA | A <-- not(A) + 1 | Example | 00 000 1001 00 | ---- | ---- | PC_out+1 |

| 20 | Jmp | PC <-- Operand | Example | 00 000 0010 XX | ---- | ---- | Depends |

| 21 | JmpZ | if Z = 1: PC <-- Operand | Example | 00 000 0010 XX | ---- | ---- | Depends |

| 22 | JmpOV | if OV = 1: PC <-- Operand | Example | 00 000 0010 XX | ---- | ---- | Depends |

| 23 | JmpC | if C = 1: PC <-- Operand | Example | 00 000 0010 XX | ---- | ---- | Depends |

| 24 | Jmp_rel | PC <-- PC + Operand | Example | 00 000 0010 XX | ---- | ---- | Depends |

| 25 | JMPEQ | if EQ = 1: PC <-- Operand | Example | 00 000 0010 XX | ---- | ---- | Depends |

| 26 | ClearZ | Z <--- 0 | Example | 00 000 0010 XX | ---- | ---- | PC_out+1 |

| 27 | ClearOV | OV <--- 0 | Example | 00 000 0010 XX | ---- | ---- | PC_out+1 |

| 28 | ClearC | C <--- 0 | Example | 00 100 0010 XX | ---- | ---- | PC_out+1 |

| 29 | ClearACC | ACC <-- 0 | Example | 00 000 1101 XX | ---- | ---- | PC_out+1 |

| 30 | LoadPC | PC <---- A | Example | 00 000 0010 XX | ---- | ---- | A |

| 31 | SavePC | A <---- PC | Example | 00 000 0011 01 | PC | ---- | PC_out+1 |

| 32 | Load_A_Mem | A <-- Mem[Operand] | Example | 00 000 0011 00 | ---- | Operand | PC_out+1 |

| 33 | Store_A_Mem | Mem[Operand] <-- A | Example | 00 000 0010 XX | ---- | Operand | PC_out+1 |

| 34 | Load_B_Dir | B <-- Operand | Example | 01 000 0010 XX | Operand | ---- | PC_out+1 |

| 35 | Load_B_Mem | B <-- Mem[Operand] | Example | 11 000 0010 XX | ---- | Operand | PC_out+1 |

| 36 | PUSH | Mem [0 + SP] <--- A,SP <--- SP + 1 | Example | 00 000 0010 XX | ---- | SP | PC_out+1 |

| 37 | POP | A <--- Mem [0 + SP - 1],SP <--- SP - 1 | Example | 00 000 0011 00 | ---- | SP - 1 | PC_out+1 |

| 38 | NOP | NOP | Example | 00 000 0010 XX | ---- | ---- | PC_out+1 |

| 39 | HALT | HALT | Example | 00 000 0010 XX | ---- | ---- | PC |

Other instructions implementation

the follwoing instructions can be also implemented with the ones in IS:

- Call "function_name":

PUSH SavePC Push Jmp "function address" POP

- Return:

POP Add_A_Dir 4 LoadPC

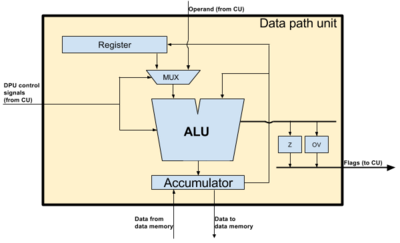

DataPath unit

Flags

- Zero Flag (Z)

- Overflow Flag (OV):

- Carry Flag (C):

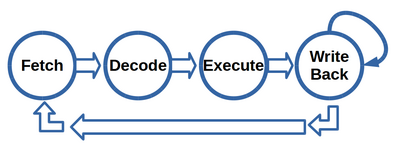

Control unit

]File:InstDec.png

400px

Instruction Memory (ROM)

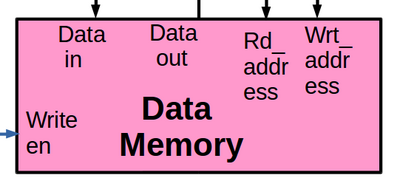

Data Memory

Functional Testing

Assembler

Python Assembly translator

A simple assembly translator was designed to make debugging process faster. Here you can see 32 bit version of the code:

import re

InstructionOpCode = {

'Add_A_B': "000000",

'Add_A_Mem': "000001",

'Add_A_Dir': "000010",

'Sub_A_B': "000011",

'Sub_A_Mem': "000100",

'Sub_A_Dir': "000101",

'IncA': "000110",

'DecA': "000111",

'And_A_B': "001000",

'OR_A_B': "001001",

'XOR_A_B': "001010",

'FlipA': "001011",

'NegA': "001100",

'Jump': "001101",

'JmpZ': "001110",

'JmpOV': "001111",

'Jmp_rel': "010000",

'JMPEQ': "010001",

'ClearZ': "010010",

'ClearOV': "010011",

'LoadPC': "010100",

'SavePC': "010101",

'ShiftArithR': "010110",

'ShiftArithL': "010111",

'ShiftA_R': "011000",

'ShiftA_L': "011001",

'Load_A_Mem': "011010",

'Store_A_Mem': "011011",

'Load_B_Dir': "011100",

'Load_B_Mem': "011101",

'JmpC': "011110",

'ClearC': "011111",

'ClearACC': "100000",

'RRC': "100001",

'RLC': "100010",

'PUSH': "111100",

'POP': "111101",

'NOP': "111110",

'HALT': "111111",

}

AssemblyFile = open('Assembly.txt', 'r+')

MachineCodeFile = open('MachineCode.txt', 'w')

counter=0

for line in AssemblyFile:

for key in InstructionOpCode:

if key in line:

operand= "00000000"

if "Mem" in line:

operand = re.findall(r'\d+',line)[0]

elif "Jmp" in line:

operand = re.findall(r'\d+',line)[0]

elif "Dir" in line:

operand = re.findall(r'\d+',line)[0]

operand = "00000000"+"00000000"+"00000000"+ operand

MachineCodeFile.write(str(counter)+ " => "+ "\"00"+InstructionOpCode[key]+operand+'\",'+'\n')

counter +=1

MachineCodeFile.close()

AssemblyFile.close()

Java Assembler