Difference between revisions of "CDS LAB1"

From ATI public wiki

(→NC-Verilog Netlist'i tekitamine) |

(→NC-Verilog simulatsiooni sisendandmed=) |

||

| Line 230: | Line 230: | ||

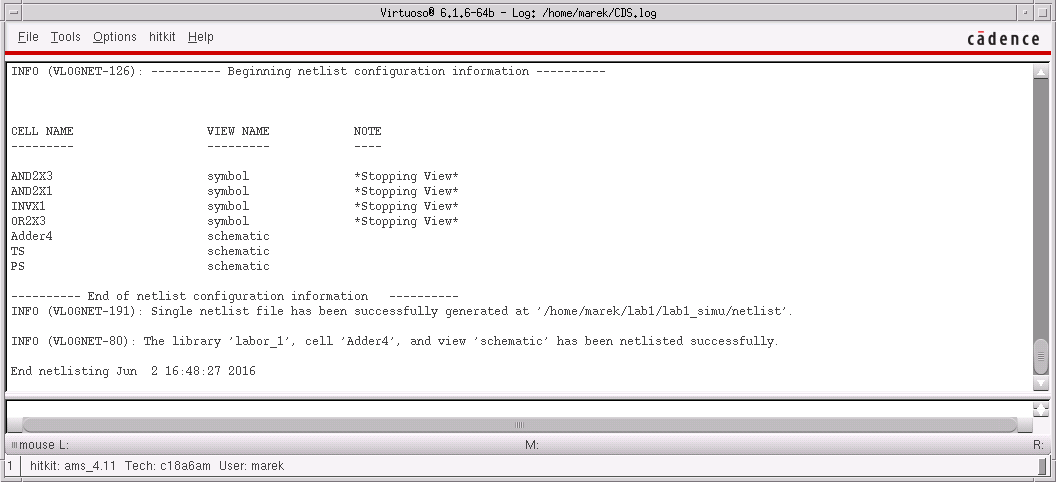

:[[File:Cds lab1 36.png|Cadence Main Window, netlist generation output]] | :[[File:Cds lab1 36.png|Cadence Main Window, netlist generation output]] | ||

| − | ==NC-Verilog simulatsiooni sisendandmed=== | + | ===NC-Verilog simulatsiooni sisendandmed=== |

et simulaatoril oleks mida simuleerida on meil vaja sisendandmeid | et simulaatoril oleks mida simuleerida on meil vaja sisendandmeid | ||

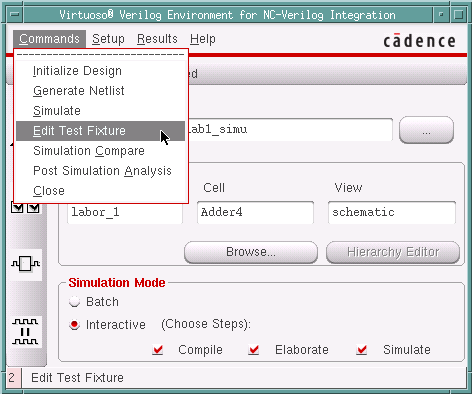

selleks võtame '''NC-Verilog''' põhiakna '''Commands''' menüüst valiku '''Edit Test Fixture''' | selleks võtame '''NC-Verilog''' põhiakna '''Commands''' menüüst valiku '''Edit Test Fixture''' | ||

:[[File:Cds lab1 37.png|Cadence NC-Verilog Edit Test Fixture]] | :[[File:Cds lab1 37.png|Cadence NC-Verilog Edit Test Fixture]] | ||

Revision as of 17:14, 2 June 2016

Tutoriali eesmärk on viia läbi digitaalskeemi koostamine ja simulatsioon kasutades Cadence vahendeid

Contents

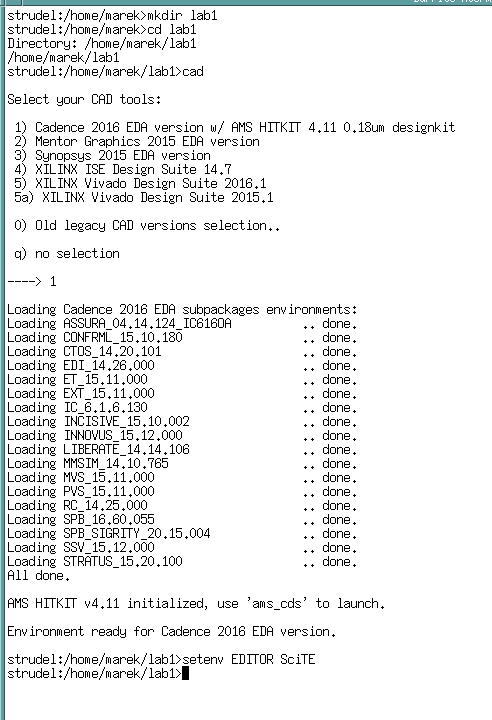

Sätime paika oma töökeskkonna

kõik selles ja järgmises lõigus olevad tegevused toimuvad käsurealt

- loome uue alamkataloogi lab1

- liigume sinna alamkataloogi

- kasutades käsku 'cad' ja sealt valikuga '1' väärtustame kõik vajalikud keskkonnamuutujad Cadence jaoks

- seejärel vahetame ümber tekstiredaktori vaikeväärtuse, valides uueks tekstiredaktoriks SciTE, vaikimisi on tekstiredaktoriks vi

Käivitame Cadence

- Cadence 2016 EDA ver. juhist jälgides

- kui on tegemist esmakordse käivitamisega siis kasutame käsurida

-

ams_cds -64 -tech c18a6 -add CORELIB -add IOLIB_6AM -add GATES_ANA

- siin me valisime tehnoloogiaks AMS 0.18μm tehnoloogia 6 metallikihiga ja lisasime elementbaaside kataloogide nimistusse kolm täiendavat kataloogi

- kui on tegemist järgmiste käivitamiskordadega siis kasutame käsurida

-

ams_cds

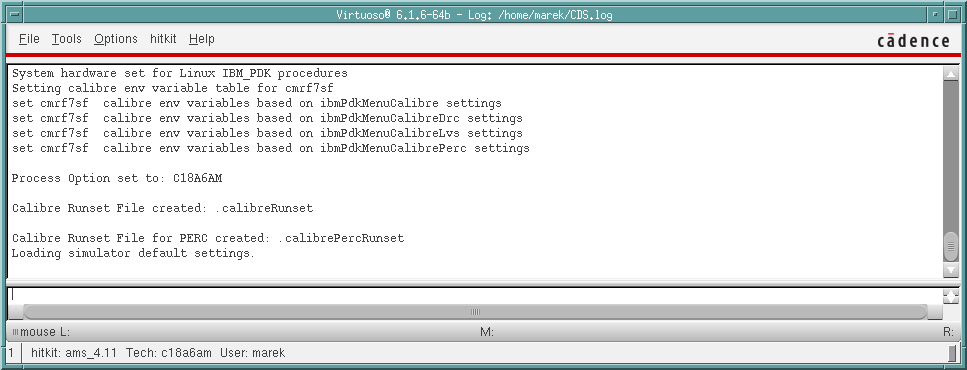

- peale ülevalpool oleva pildi teateid võib käsurida ignoreerida, edasised tegevused toimuvad läbi Cadence graafilise kasutajaliidese

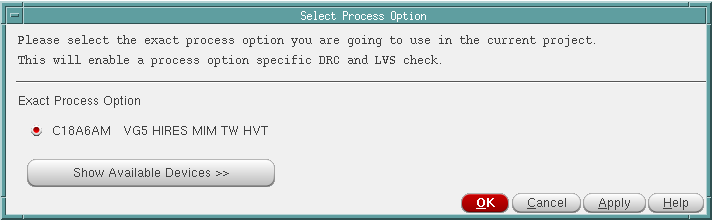

- avaneb mitmeid akneid, ühel neist küsitakse täpsustavat informatsiooni meil kasutatava designkit'i kohta

- siin õnneks on ainult üks valik ja tuleks vajutada nupule OK

- avaneb ka Cadence põhiaken mis vaikimisi paikneb töölaual vasakul alumise nurga juures

- siia kogunevad Cadence teated , sealhulgas ka veateated

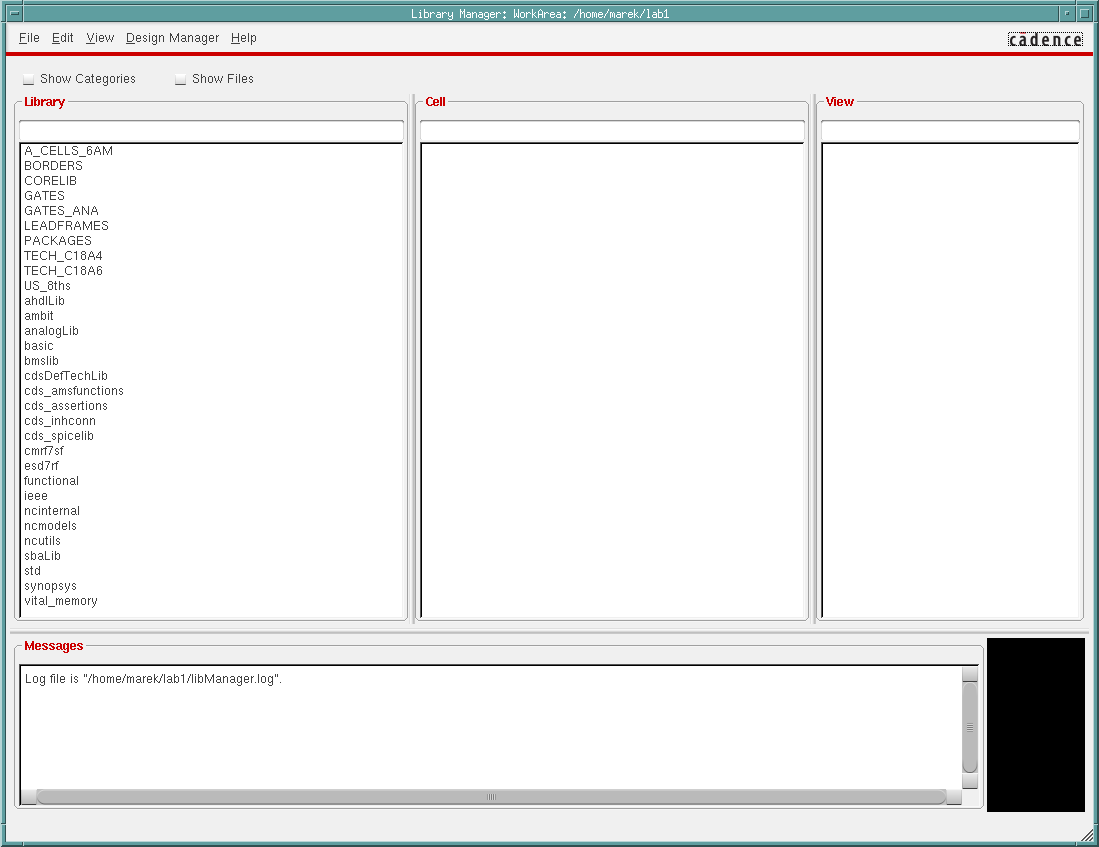

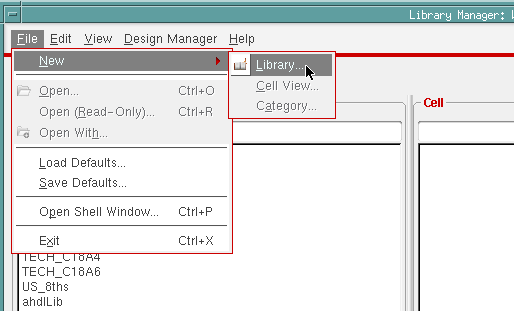

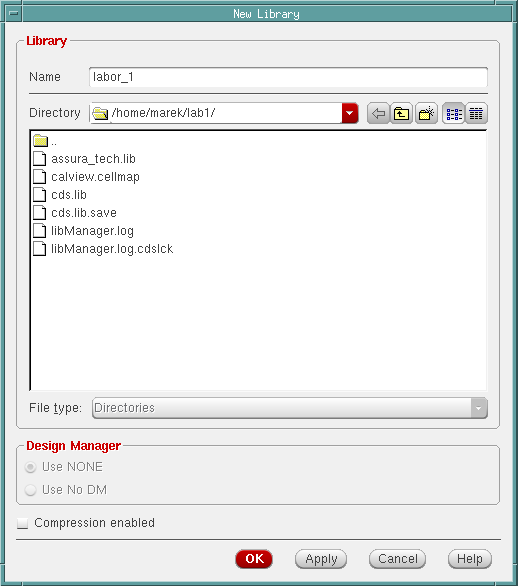

Tekitame oma library

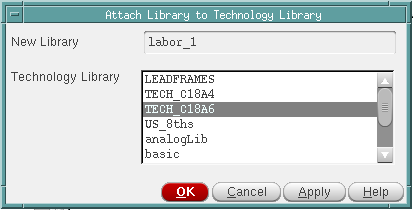

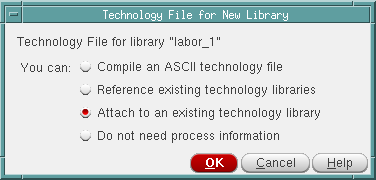

- avaneb uus väike aken küsimusega ja valikvastustega, valime Attach to an existing technology library ja vajutame OK

Tekitame uue skeemi oma library'sse

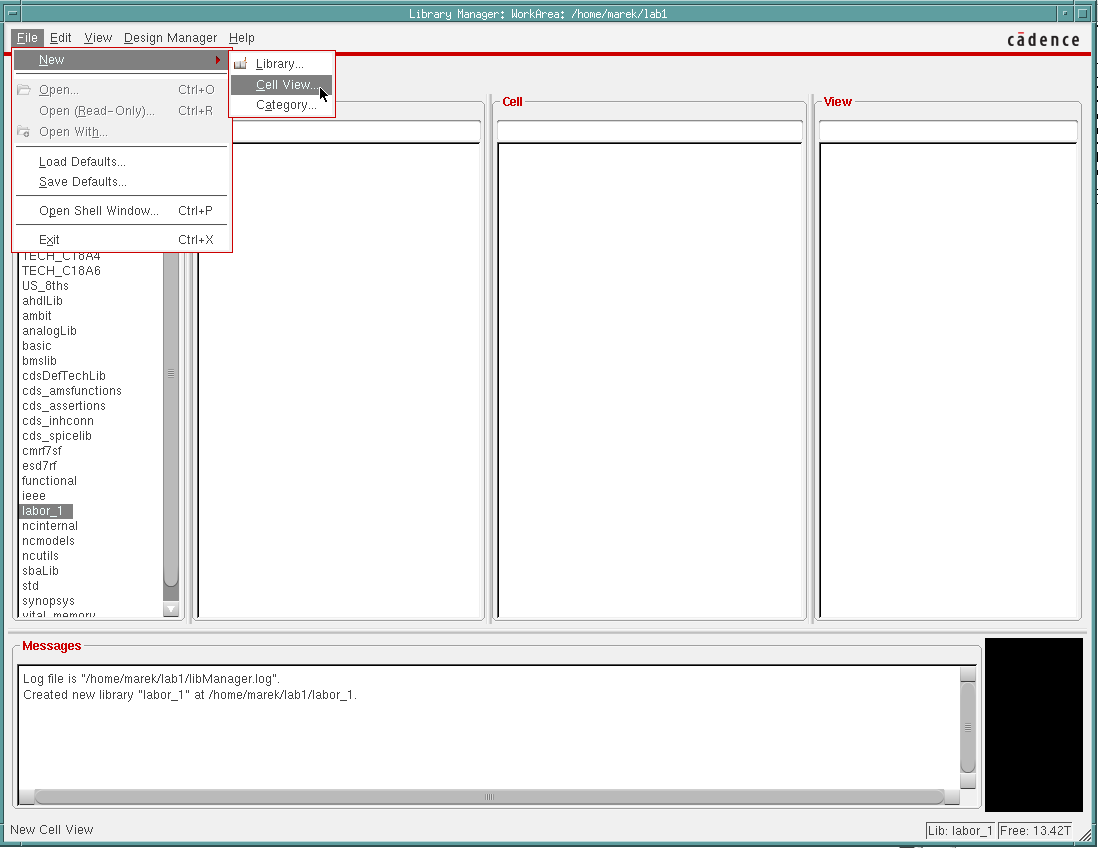

- selleks tuleb Library Manager aknas ära valida library millele me andsime nime labor_1 ja valida menüüst File valik New ning Cell View

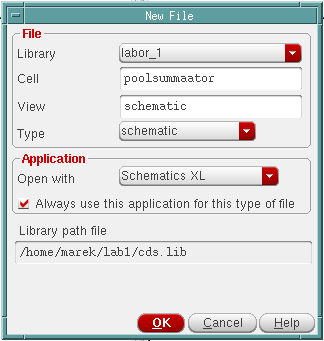

- avanevas aknas täidame välja Cell andes oma uuele skeemile nimeks poolsummaator

- Application valikute osas valime Schematics XL ja märgime ära checkbox'i Always use this application for this type of file

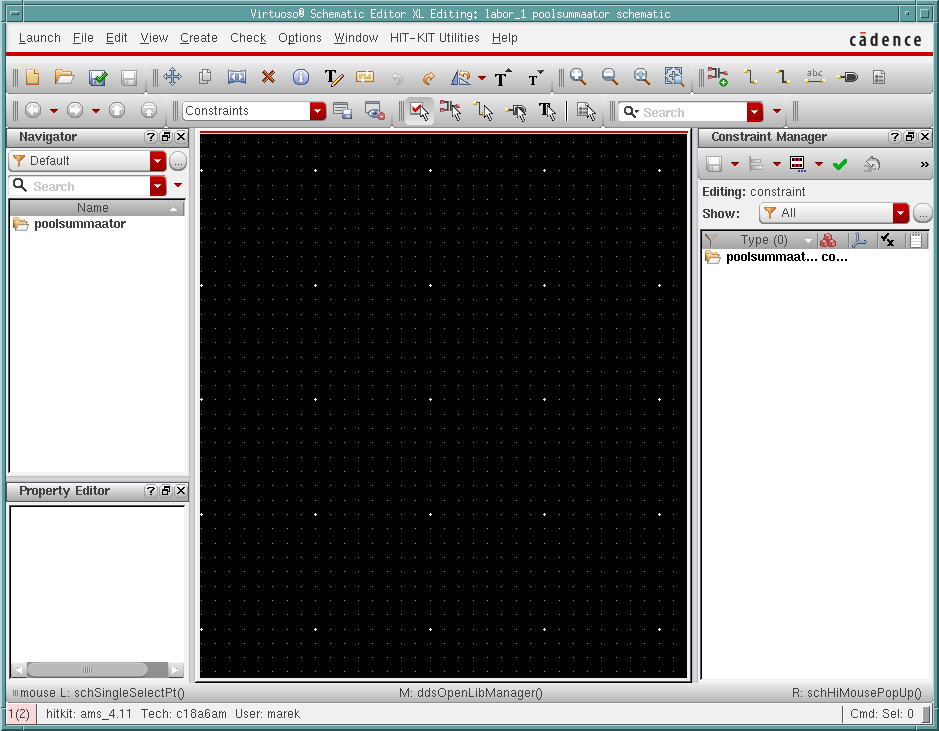

- ja vajutame OK , selle peale avaneb meile skeemiredaktori aken

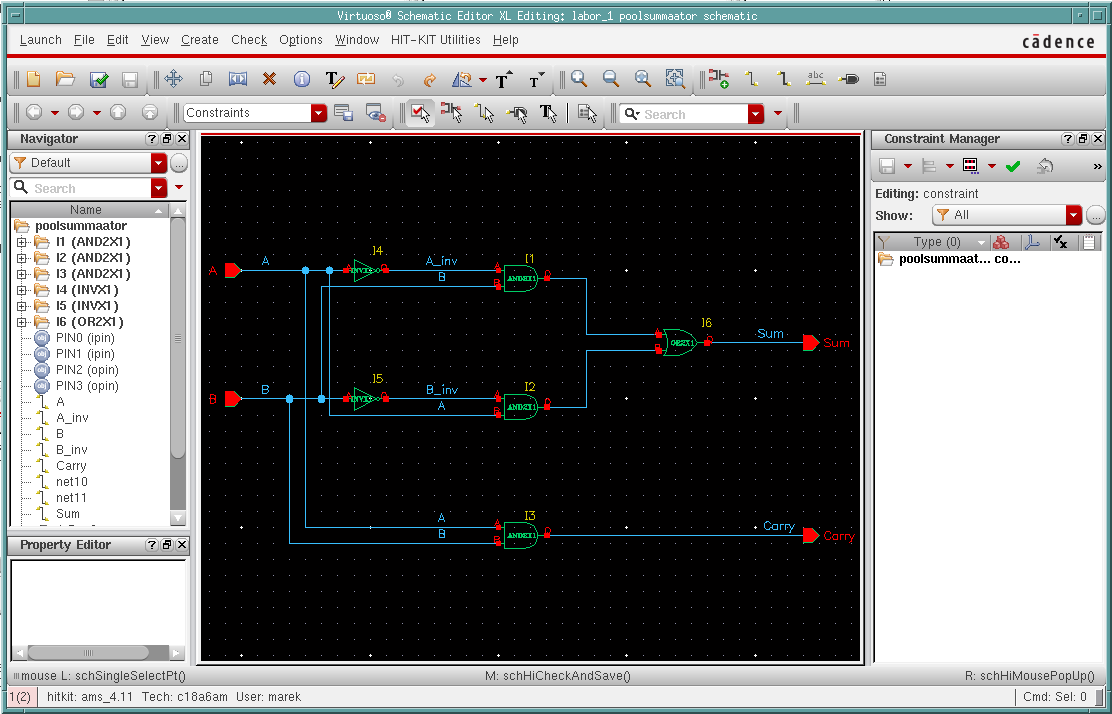

Poolsummaatori skeemi redigeerimine

- siinkohas on mõislik meelde jätta mõned skeemiredaktori lühikäsud

- 'i' - instance , uue skeemielemendi lisamiseks

- 'w' - wire , uue ühenduse loomiseks

- 'l' - label , ühendusele nime panemine

- 'p' - pin , uue sisendi/väljundi loomiseks

- 'f' - fit to view , mahutab kogu seni joonistatud skeemi meie vaatevälja

- 'u' - undo , viimase tegevuse tühistamine

- 'X' - Check and Save' , teostab skeemile veakontrolli ja salvestab skeemi

- hiire paremat klahvi all hoides saab tirida piirkonna mida suurendatakse, et suurendusest kiirelt välja minna vajutada f

- igast sisestusrežiimist (instance/wire/pin/jms.) saab kiirelt väljuda klahviga ESC

- olles wire režiimis saab kindlaid ühendusi luua klahviga 's' ehk snap , selleks liikuda hiirekursoriga sobiliku ühenduspunkti lähedale ja Cadence pakub võimalikku ühenduse loomist kollase rombi kujulise kastiga selle punkti ümber

- NB! undo töötab kuni viimase salvestuseni, peale salvestust ei ole võimalik skeemi tehtud muudatusi tagasi võtta

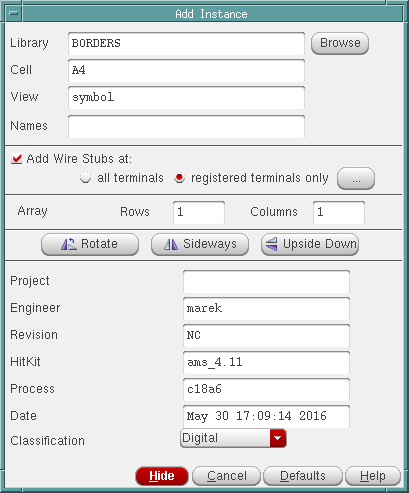

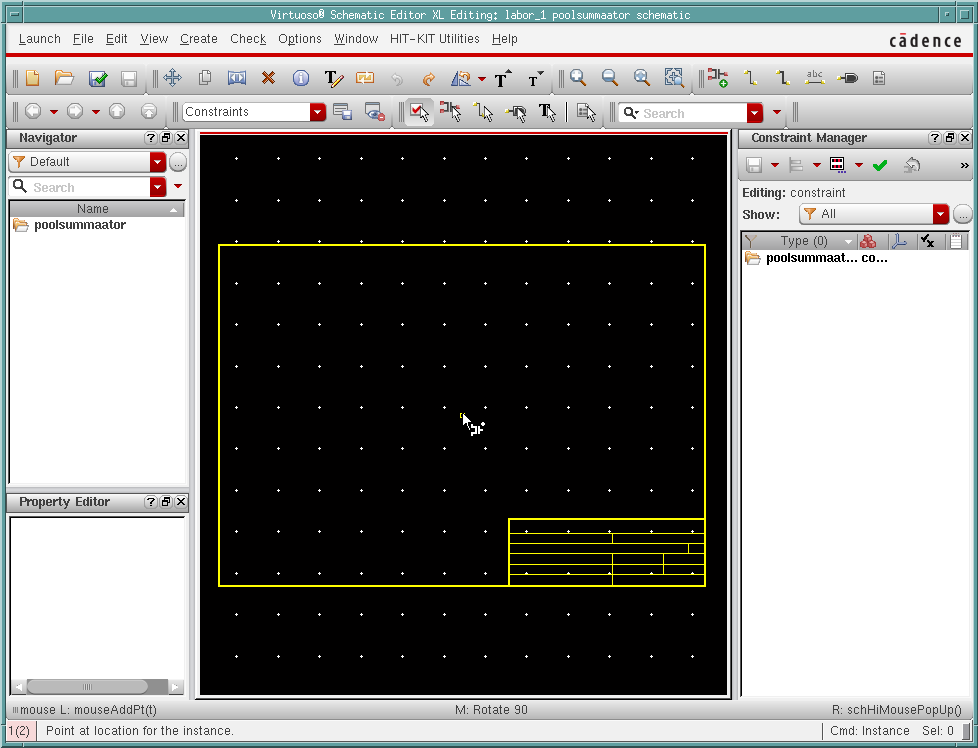

Kirjanurgaga raami lisamine

- vajutame klahvi i ja avanevas aknas nuppu Browse

- avaneb Library Browser kus valime Library alt BORDERS ja sealt Cell alt A5

- täindavalt avanenud Library Manager akna võime sulgeda vajutades nupule Close

- Add Instance akna saame ajutiselt ära peita vajutades nupule Hide

- seejärel liikudes hiirekursoriga skeemiredaktori akna mustale alale saame valitud elemendi paika panna

- Cadence pakub kollase raamiga võimalikku asukohta, sobival kohal elemendi paigutamiseks vajutame hiire vasakut klahvi

- antud juhul on suvaline asukoht sobiv nii, et vajutame hiire vasakut klahvi

- seejärel tuleks fit to view teha ehk vajutame klahvi f

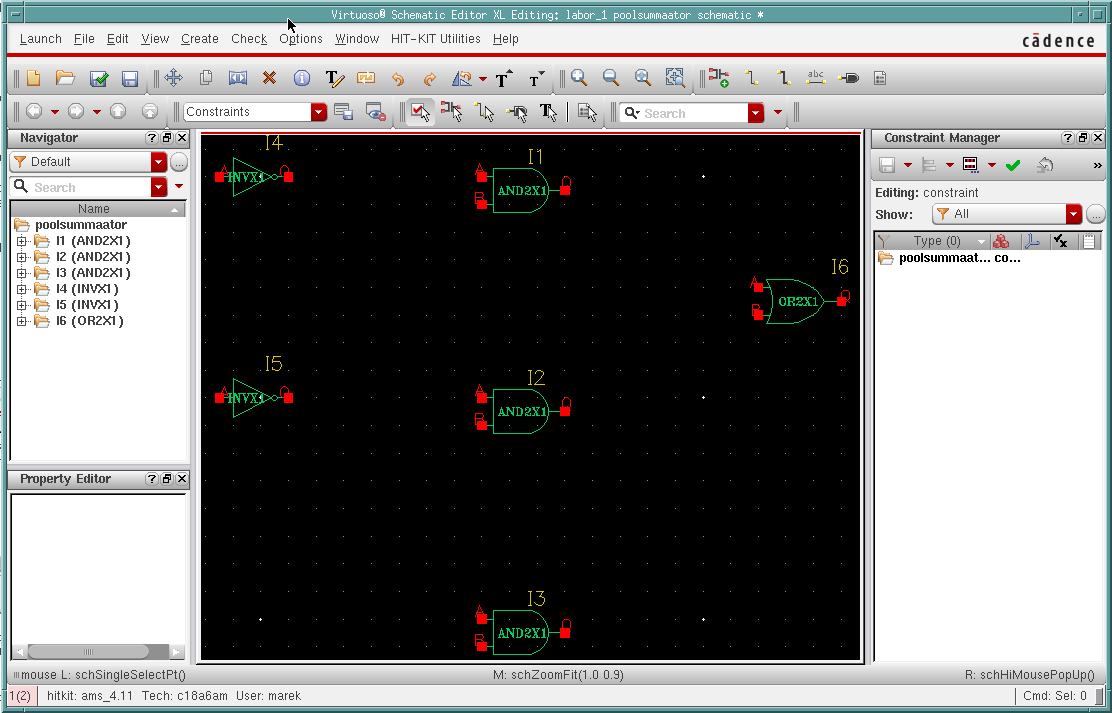

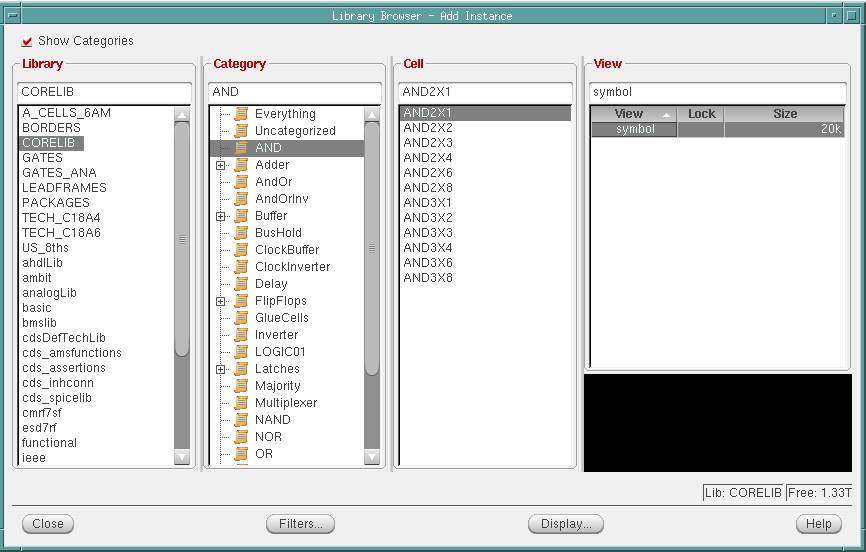

Poolsummaatori skeemielementide lisamine

- vajutame klahvi i ja avanevas aknas nuppu Browse

- avaneb Library Browser kus valime Library alt CORELIB

- meile vajalikud skeemielemendid asuvad siis library nimega CORELIB all

- kõigepealt on meil vaja mõned AND elemendid paika panna

- selleks valime Category alt AND ja Cell alt AND2X1

- tähe-numbri kombinatsioon elemendi nime taga näitab mitu sisendit sellel on ning mis võimsusega on väljund (mitu järgmist sisendit on väljund suuteline ära toitma)

- antud juhul on tegemist kahe sisendiga AND elemendiga mille väljundvõimsus on 1

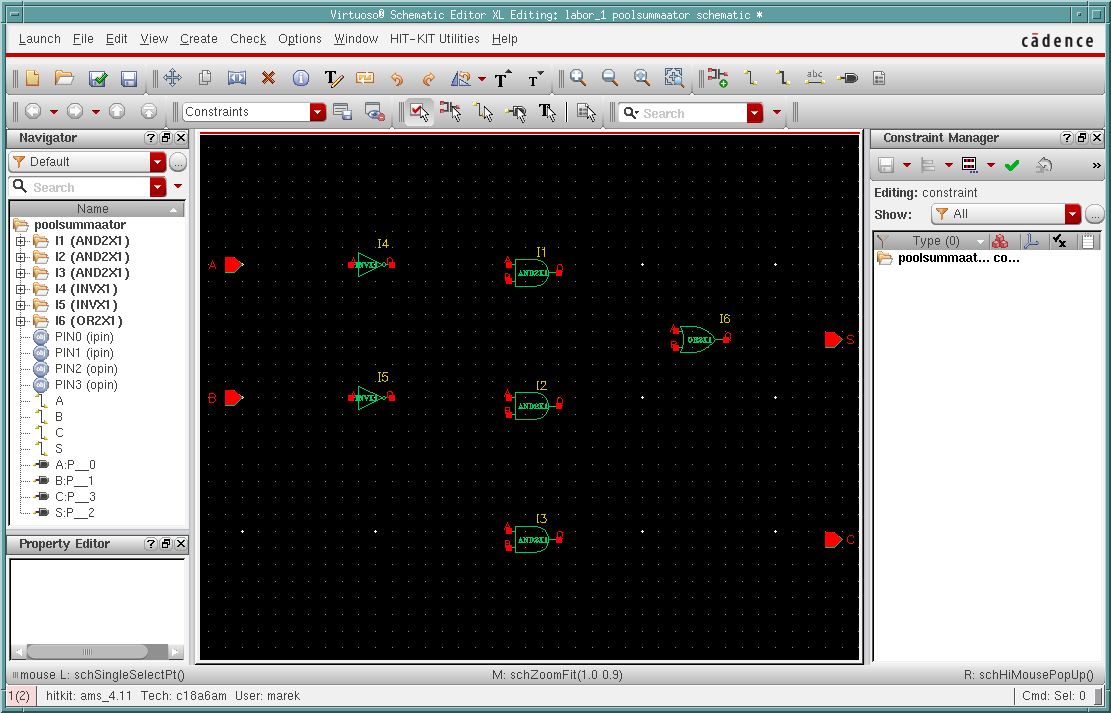

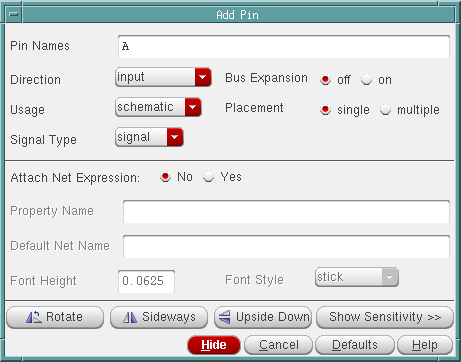

Poolsummaatori skeemi sisendite ja väljundite lisamine

- lisame skeemile sisendid ja väljundid ehk pin'id , selleks vajutame klahvi p

- esimeseks nimeks (Pin Name) valime A ja suunaks (Direction) valime input

- pin'ide paigutamine toimub sama moodi nagu elementide paigutamine

Poolsummaatori skeemielementide vaheliste ühenduste loomine

- tekitame skeemielementide vahelised ühendused, selleks vajutame klahvi w ning snap'i kasutades ühendame elemendid omavahel

- skeemi parema jälgitavuse huvides võib ühendustele paigutada nimed nagu ülevalpool oleval pildil, selleks vajutada klahvi l

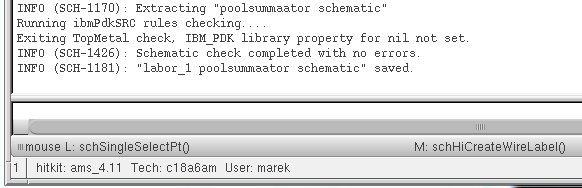

Poolsummaatori skeemi salvestamine

- salvestamiseks vajutame klahvi X

- Cadence põhiaknast võib jälgida vigade kontrolli ja salvestuse tulemust

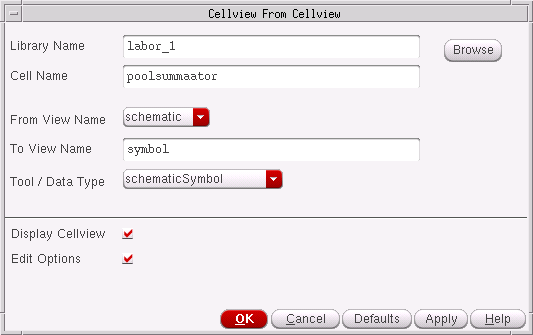

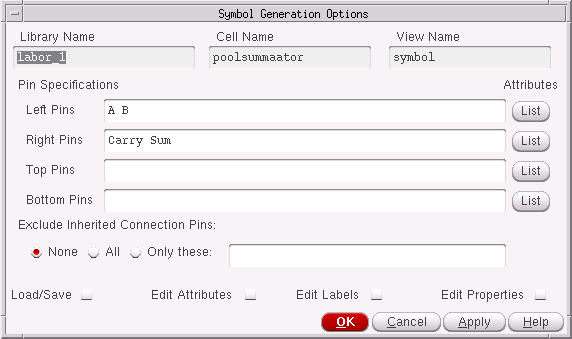

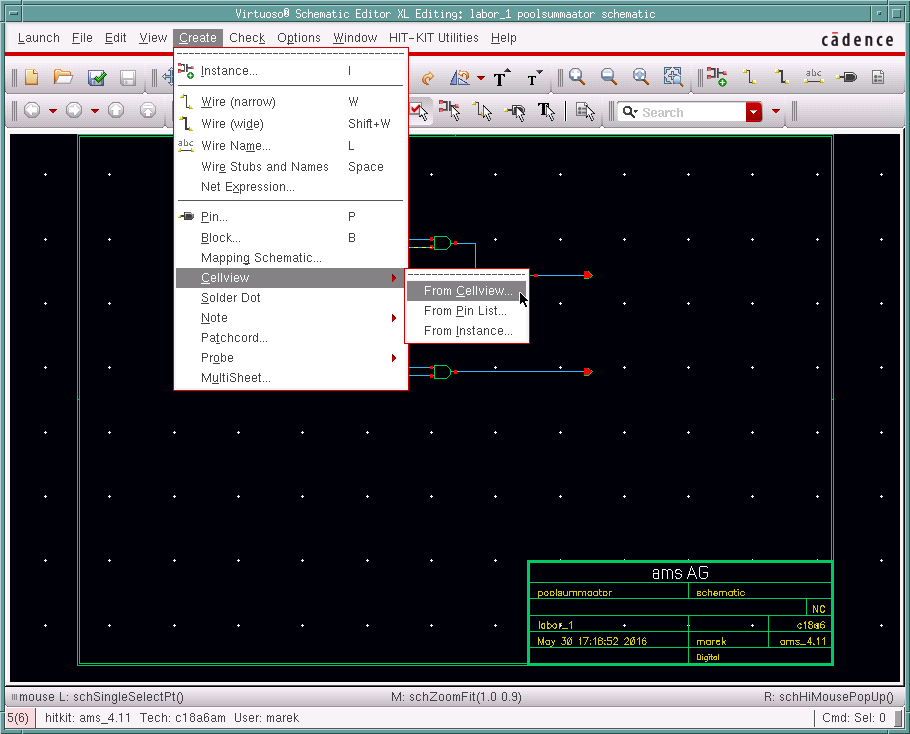

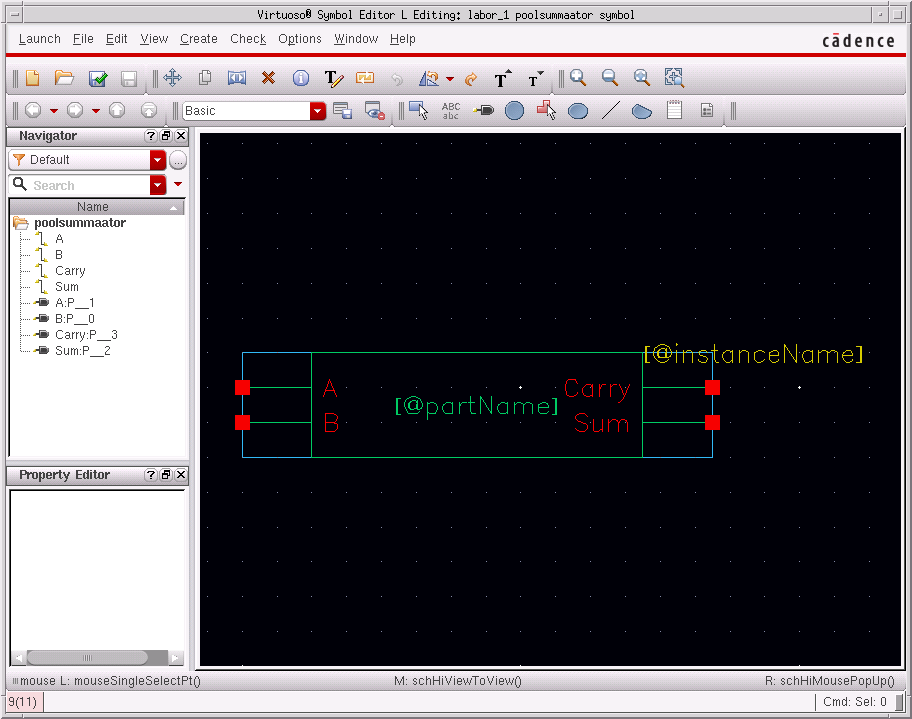

Poolsummaatori sümboli loomine (makro tegemine)

- et meie valminud skeemi kasutada muude skeemide joonistamisel makrona, tuleb teha skeemile uus 'symbol' vaade

- selleks valime menüüst Create valiku Cellview ja alamvaliku From Cellview

- avaneb Cadence Symbol Editor aken

- automaatselt tekitatud sümbol on kastikujuline , kasutajal on võimalik tööriistaribal olevate primitiivide kaudu seda kujundada endale sobivaks

Täissummaator kahest poolsummaatorist

- eelnevas peatükis koostatud poolsummaatori primitiivi kasutades saame luua täissummaatori

- ka sellest teeme makro ehk loome sümboli et saaksime seda kasutada edasistes skeemides

- skeemi sees saab vajadusel laskuda makro sisse, selleks kas

- teeme makroelemendi peal hiirega topeltkliki

- valime makroelemendi ja kasutame käsklust Descend Edit mille lühikäskluseks on klahvikombinatsioon Shift + E

- et tagasi eelmisele tasemele tulla kasutame käsklust Return mille lühikäskluseks on klahvikombinatsiooon Ctrl + E

- skeemi sees laskumine võib osutuda vajalikuks näiteks juhul kui meil on vaja muuta makro väljundite väljundvõimsust

- NB! muutes ühe makro sisu muutub see kohe igal pool kus seda makrot kasutatud on

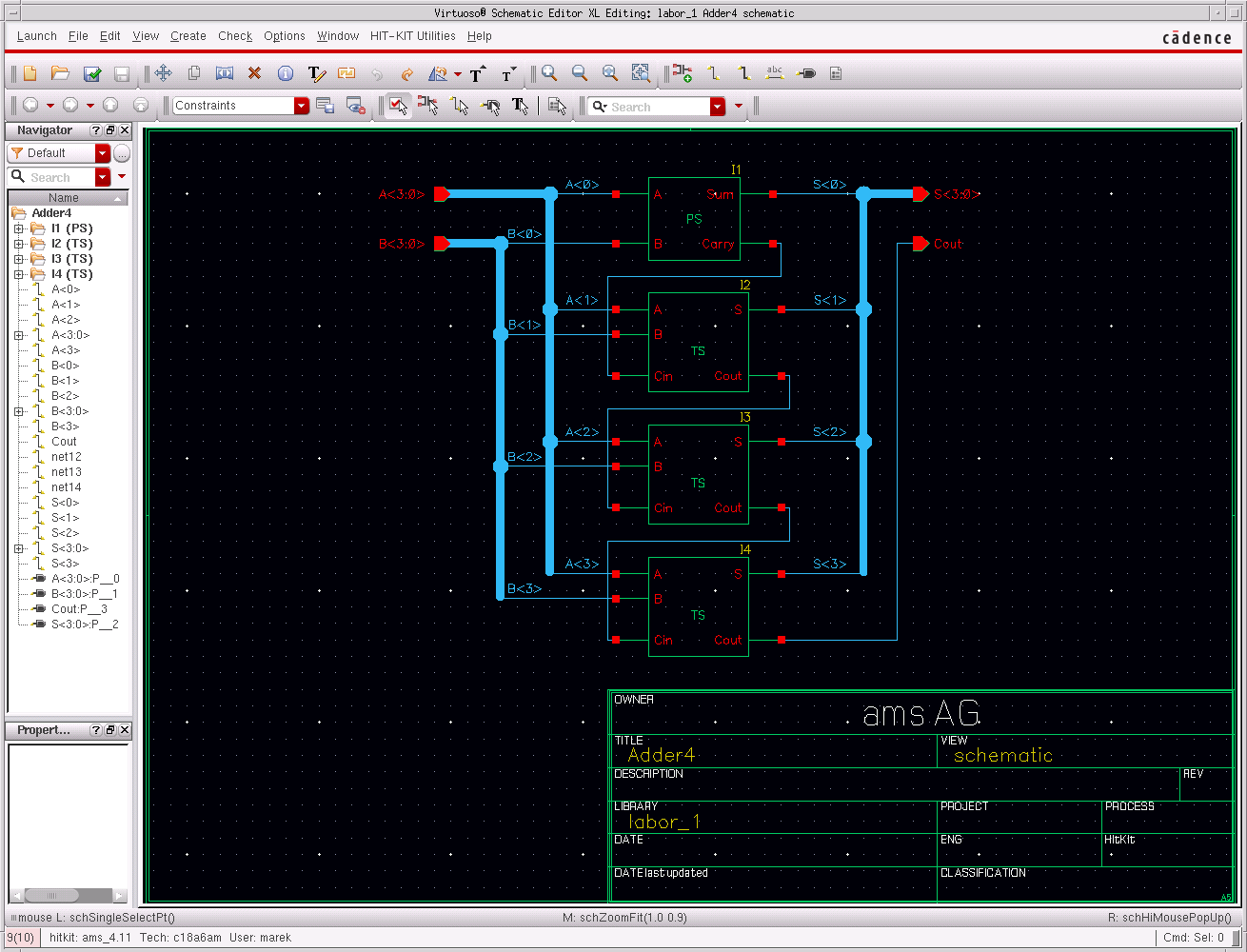

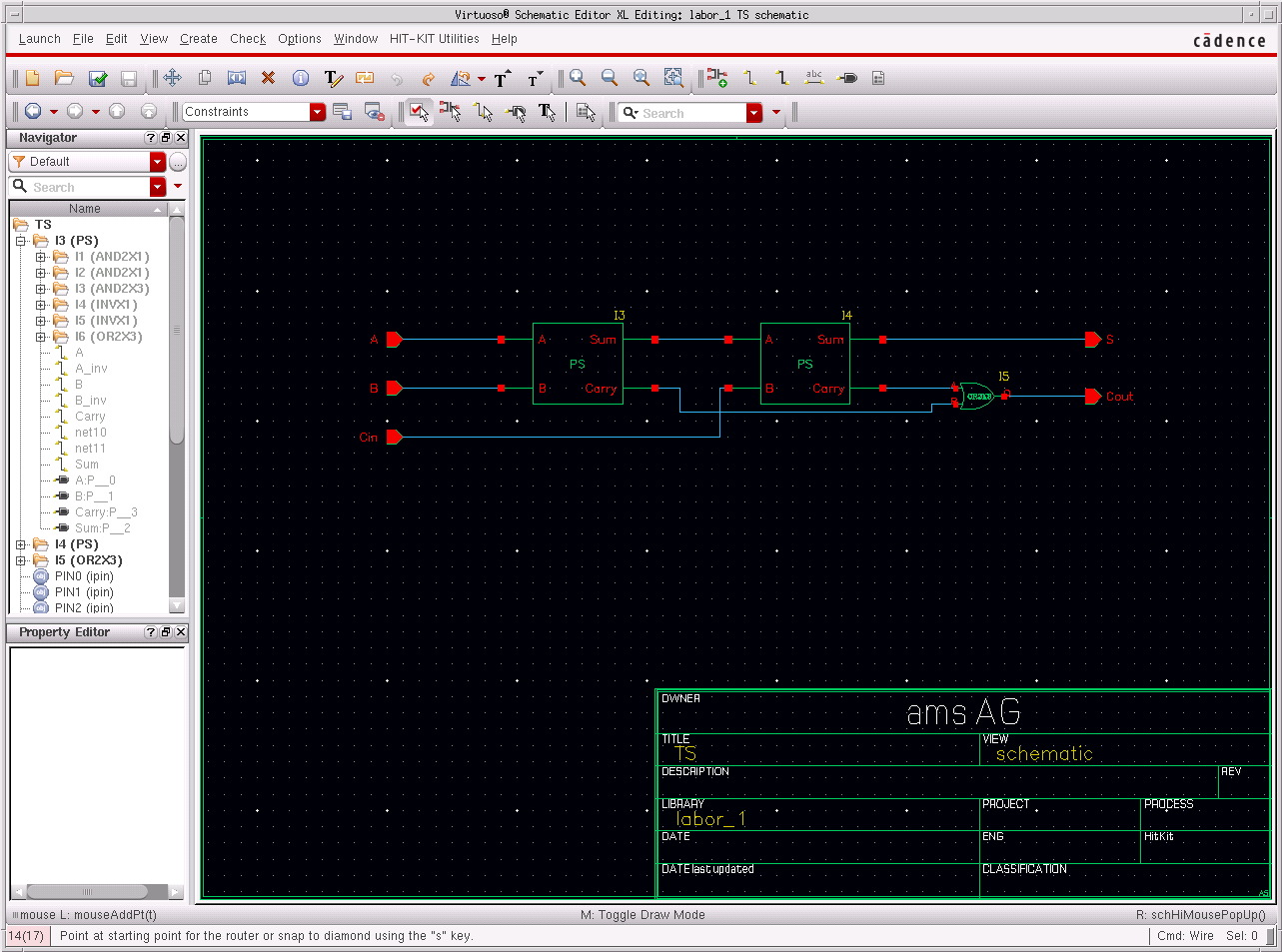

4 bitine liitja

- et meil on kõik vajalikud komponendid nüüd olemas, siis saame asuda 4 bitise liitja koostamise juurde

- komponentidena läheb meil vaja ühte poolsummaatorit ja kolme täissummaatorit

- ülekandeahela lahendame antud skeemis jadaülekandega ehk ingl. Riple Carry

- et tegemist on pisikese 4-bit liitjaga siis jadaülekanne on meile sobiv, suuremate liitjate juures on mõistlik kasutada rööpülekannet, näiteks Lynch-Swartzlander Spanning Tree Carry Lookahead

- selle skeemi juures kasutame juba andmesiine, antud juhul 4-bitiseid

- et andmesiinid oleks paremini nähtavad kasutame nende joonistamiseks jämedat ühendust

- andmesiinidelt eraldi bittide väljatoomine ja ühendamine toimub läbi ühendustele nimede andmise

4bit liitja simulatsioon

- nüüd kus meil on skeem valmis ja kontrollitud ning salvestatud, hakkame seda simuleerima digitaalsimulatsiooniga

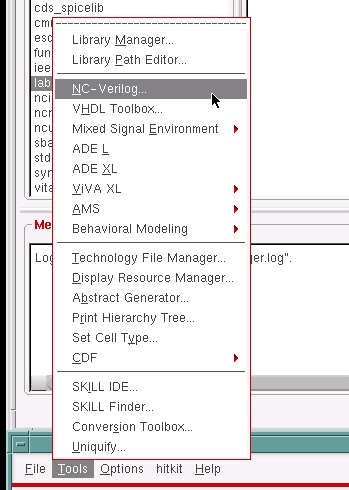

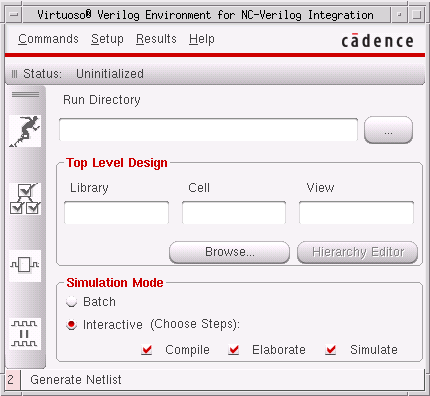

NC-Verilog avamine

- avaneneb uus aken

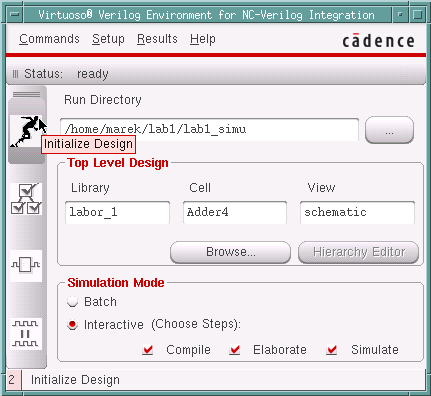

- siin tuleb mõned asjad paika sättida:

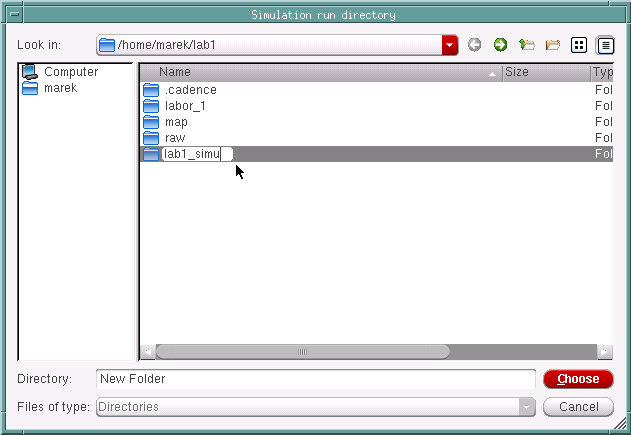

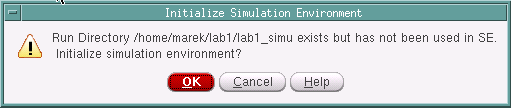

- Run Directory - vajutame kolme punktiga nupule ja valime endale sobiva töökataloogi (antud juhul tuleb meil töökataloog alles tekitada , antud näites lab1_simu)

- disain valida, selleks vajutame Browse peale ning avanevast Library Browser'ist valime oma skeemi ja schematic vaate

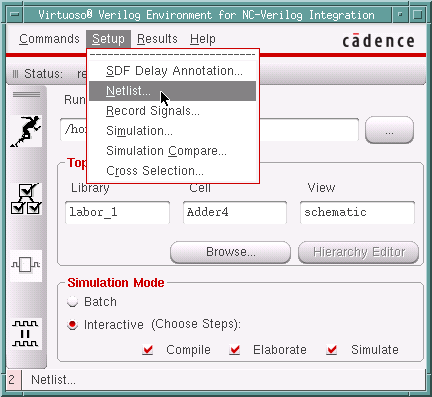

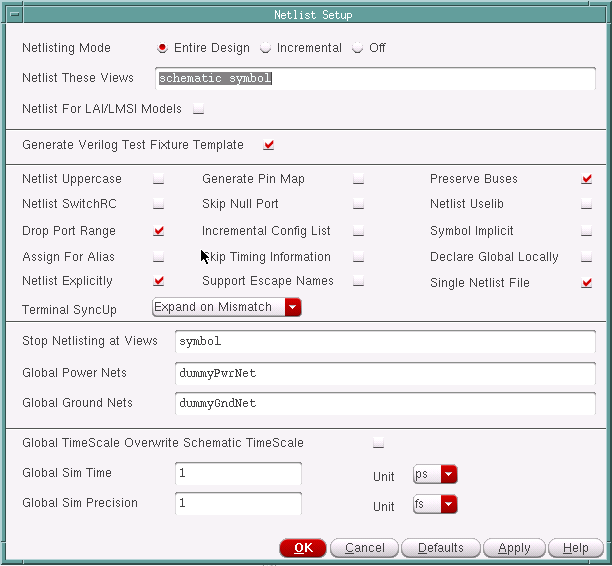

NC-Verilog initsialiseerimine ja sätted

- avaneb menüü

- siin sätime järgnevat

- Netlist These Views valime schematic symbol

- valime Single Netlist File

- Global Sim Time valime 1 ja ühikuks ps

- Global Sim Precision valime 1 ja ühikuks fs

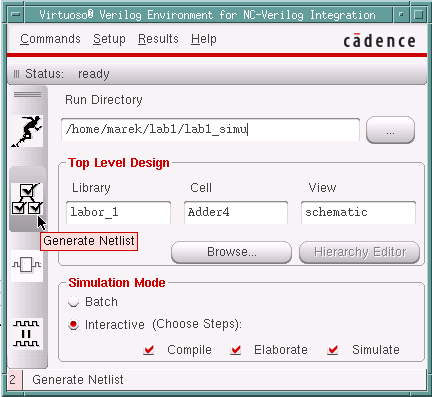

NC-Verilog Netlist'i tekitamine

- järgmise sammuna tuleb meie skeemile netlist tekitada, selleks vajutame NC-Verilog põhiakna vasakul ribal järgmist nuppu Generate Netlist

NC-Verilog simulatsiooni sisendandmed

et simulaatoril oleks mida simuleerida on meil vaja sisendandmeid selleks võtame NC-Verilog põhiakna Commands menüüst valiku Edit Test Fixture