# **DOCTORAL THESIS**

# Hardware Realization of Lattice-based Post-Quantum Cryptography

Malik Imran

TALLINNA TEHNIKAÜLIKOOL TALLINN UNIVERSITY OF TECHNOLOGY TALLINN 2023 TALLINN UNIVERSITY OF TECHNOLOGY DOCTORAL THESIS 33/2023

# Hardware Realization of Lattice-based Post-Quantum Cryptography

MALIK IMRAN

TALLINN UNIVERSITY OF TECHNOLOGY School of Information Technologies Department of Computer Systems

The dissertation was accepted for the defence of the degree of Doctor of Philosophy in Information and Communication Technologies on July 31 2023

| Supervisor: | Prof. Dr. Samuel Pagliarini,<br>Department of Computer Systems, Centre for Hardware Security,<br>Tallinn University of Technology,<br>Tallinn, Estonia |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| Opponents:  | Prof. Georg Sigl,<br>Technical University of Munich,<br>Munich, Germany                                                                                |

|             | Prof. Francesco Regazzoni,<br>University of Amsterdam,<br>Amsterdam, The Netherlands                                                                   |

#### Defence of the thesis: August 29 2023, Tallinn

#### Declaration:

Hereby I declare that this doctoral thesis, my original investigation and achievement, submitted for the doctoral degree at Tallinn University of Technology, has not been submitted for any academic degree elsewhere.

Malik Imran

.....

signature

Copyright: Malik Imran, 2023 ISSN 2585–6898 (publication) ISBN 978-9916-80-029-4 (publication) ISSN 2585–6901 (PDF) ISBN 978-9916-80-030-0 (PDF) Printed by Koopia Niini & Rauam TALLINNA TEHNIKAÜLIKOOL DOKTORITÖÖ 33/2023

# Võrel põhinev post-kvant-krüptograafia riistvaraline realisatsioon

MALIK IMRAN

# Contents

| Lis | List of Publications                                                                                                                                                                                                                                                                                                                                            |                                              |  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|--|

| Ab  | Abbreviations                                                                                                                                                                                                                                                                                                                                                   |                                              |  |

| 1   | oduction<br>Novelty, Contributions & Summary of the Thesis                                                                                                                                                                                                                                                                                                      |                                              |  |

| 2   | <ul> <li>2 Background</li></ul>                                                                                                                                                                                                                                                                                                                                 |                                              |  |

| 3   | <ul> <li>A Generator of Large Integer Polynomial Multipliers</li></ul>                                                                                                                                                                                                                                                                                          | 35<br>37<br>38<br>43                         |  |

| 4   | <ul> <li>Design Space Exploration of SABER</li> <li>4.1 Serial and Parallel SABER Architectures</li> <li>4.1.1 Memory Manager</li> <li>4.1.2 Pipelining</li> <li>4.1.3 Shared Shift Buffer</li> <li>4.1.4 Address Decoder Unit (ADU)</li> <li>4.1.5 SABER Building Blocks</li> <li>4.2 Implementation Results</li> <li>4.3 Comparison and Discussion</li> </ul> | 50<br>52<br>53<br>54<br>54<br>54<br>54<br>60 |  |

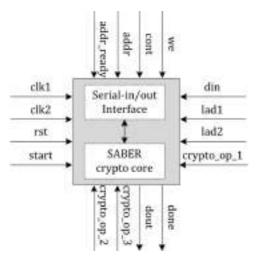

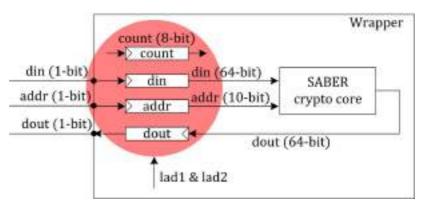

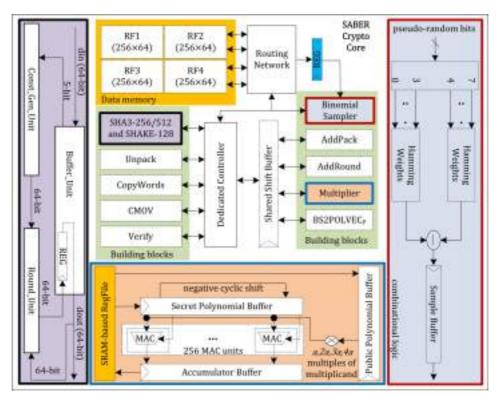

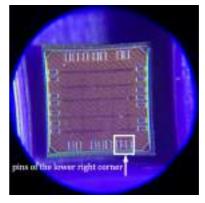

| 5   | <ul> <li>High-Speed SABER Chip Design</li></ul>                                                                                                                                                                                                                                                                                                                 | 71<br>71<br>72<br>73<br>74<br>75<br>76<br>76 |  |

| 6   | Conclusions and Future Directions                                                                                                                                                                                                                                                                                                                               | 81                                           |  |

| Lis | st of Figures                                                                                                                                                                                                                                                                                                                                                   | 84                                           |  |

| Lis | List of Tables                                                                                                                                                                                                                                                                                                                                                  |                                              |  |

| Re  | eferences                                                                                                                                                                                                                                                                                                                                                       | 86                                           |  |

| cknowledgements | 97 |

|-----------------|----|

| ostract         | 98 |

| opendix 1       | )3 |

| opendix 2       | 31 |

| opendix 313     | 39 |

| opendix 415     | 59 |

| opendix 5       | 57 |

| opendix 61      | 75 |

| urriculum Vitae | 38 |

| ulookirjeldus   | 39 |

# List of Publications

The present Ph.D. thesis is based on the following publications that are referred to in the text by Roman numbers.

- I M. Imran, Z. U. Abideen, and S. Pagliarini, "An experimental study of building blocks of lattice-based nist post-quantum cryptographic algorithms," *Electronics*, vol. 9, no. 11, 1953, 2020. DOI: https://doi.org/10.3390/ electronics9111953

- II M. Imran, Z. U. Abideen, and S. Pagliarini, "An open-source library of large integer polynomial multipliers," in 2021 24th International Symposium on Design and Diagnostics of Electronic Circuits & Systems (DDECS), Vienna, Austria, 2021, pp. 145–150. DOI: https://doi.org/10.1109/DDECS52668.2021.9417065

- III M. Imran, Z. U. Abideen, and S. Pagliarini, "A versatile and flexible multiplier generator for large integer polynomials," *Journal of Hardware and Systems Security*, 2023. DOI: https://doi.org/10.1007/s41635-023-00134-2

- IV M. Imran, F. Almeida, J. Raik, A. Basso, S. S. Roy, and S. Pagliarini, "Design space exploration of saber in 65nm asic," in Proceedings of the 5th Workshop on Attacks and Solutions in Hardware Security, ASHES '21, Virtual Event, Republic of Korea, 2021, pp. 85–90. DOI: https://doi.org/10.1145/3474376.3487278

- V M. Imran, A. Aikata, S. S. Roy, and S. Pagliarini, "High-speed design of postquantum cryptography with optimized hashing and multiplication," *IEEE Transactions on Circuits and Systems II: Express Briefs*, 2023. DOI: https://doi.org/ 10.1109/TCSII.2023.3273821

- VI M. Imran, F. Almeida, A. Basso, S. S. Roy, and S. Pagliarini, "High-speed SABER key encapsulation mechanism in 65nm CMOS." *Journal of Cryptographic Engineering*, 2023. DOI: https://doi.org/10.1007/s13389-023-00316-2

## Other related publications

- VII A. Aikata, A. C. Mert, M. Imran, S. Pagliarini, and S. S. Roy, "Kali: A crystal for post-quantum security using kyber and dilithium," *IEEE Transactions on Circuits* and Systems I: Regular Papers, vol. 70, no. 2, pp. 747–758, 2023. DOI: https://doi.org/10.1109/TCSI.2022.3219555

- VIII L. Aksoy, D. B. Roy, M. Imran, P. Karl, and S. Pagliarini, "Multiplierless design of very large constant multiplications in cryptography," *IEEE Transactions on Circuits* and Systems II: Express Briefs, vol. 69, no. 11, pp. 4503–4507, 2022. DOI: https://doi.org/10.1109/TCSII.2022.3191662

- IX F. Almeida, M. Imran, J. Raik, and S. Pagliarini, "Ransomware attack as hardware trojan: A feasibility and demonstration study," *IEEE Access*, vol. 10, pp. 44827– 44839, 2022. DOI: https://doi.org/10.1109/ACCESS.2022.3168991

- X T. Perez, M. Imran, P. Vaz, and S. Pagliarini, "Side-channel trojan insertion a practical foundry-side attack via eco," *in 2021 IEEE International Symposium on Circuits and Systems (ISCAS)*, Daegu, Korea, 2021, pp. 1–5. DOI: https: //doi.org/10.1109/ISCAS51556.2021.9401481

XI M. Imran, S. Pagliarini, and M. Rashid, "An area aware accelerator for elliptic curve point multiplication," in 2020 27th IEEE International Conference on Electronics, Circuits and Systems (ICECS), Glasgow, UK, 2020, pp. 1–4. DOI: https: //doi.org/10.1109/ICECS49266.2020.9294908

# Abbreviations

| LCM<br>LWE<br>LWR<br>LUT<br>NFS<br>NIST<br>NTT<br>NWC | Elliptic Curve Cryptography<br>Encapsulations<br>European Union Agency for Cybersecurity<br>Field-Programmable Gate Array<br>Figure-of-Merit<br>Fast Fourier Transform<br>Flip-Flop<br>International Telecommunications Union<br>Key Encapsulation Mechanism<br>Key Generation<br>Least Common Multiples<br>Learning With Errors<br>Learning With Rounding<br>Look-Up Table<br>Number Field Sieve<br>National Institute of Standards and Technology<br>Number Theoretic Transform<br>Negative Wrapped Convolution |

|-------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PKC                                                   | Public-key Cryptography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| PQC                                                   | Post-Quantum Cryptography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| PAP                                                   | Power-Area-Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| РСВ                                                   | Printed Circuit Board                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| QC                                                    | Quantum Cryptography                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RSA                                                   | Rivest, Shamir, and Adleman                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| ROM                                                   | Read Only Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RAM                                                   | Random Access Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RTL                                                   | Register-Transfer Level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SBM                                                   | Schoolbook Multiplier                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| тѕмс                                                  | Taiwan Semiconductor Manufacturing Company                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

# 1 Introduction

The world is becoming increasingly digitized and connected, and ensuring the security and privacy of sensitive information has become a critical concern for individuals and organizations. The exponential growth of the internet has opened up many opportunities, but at the same time, it has also created new challenges. Recently, in [1], the International Telecommunications Union (ITU) announced that internet users increased from 400 million (in 2000) to 4.9 billion (in 2021). According to Snowden's report [2], in 2013, this growth rate is expected to be higher. The proliferation of internet users has increased numerous data breaches and cyber attacks in recent years, which have led to the theft of sensitive information, such as personal and financial data. These incidents have not only resulted in significant financial losses but have also damaged the reputation of organizations and eroded public trust. Various security measures have been developed and implemented to address these concerns, such as encryption/decryption [3], firewalls [4], and access controls [5]. However, despite these measures, the threat of cyber attacks remains a constant, and organizations must remain vigilant and take proactive measures to protect sensitive information. Hence, the increasing connectivity of the world has highlighted the importance of data security and privacy.

Cryptography is one of the techniques to protect sensitive information using mathematical problems [6]. It transforms original information/data into a format that humans cannot understand. The original information is called plaintext, while the text obtained after some mathematical operations is a ciphertext. The sequence of operations to obtain ciphertext from plaintext and vice versa determines a cryptographic algorithm/protocol. The current cryptographic schemes are categorized into symmetric and public-key cryptography (PKC). The sender and the recipient share a common key for encrypting and decrypting the message in symmetric key cryptography. The encryption is a transformation of plaintext into ciphertext, while the conversion back from ciphertext to plaintext is a decryption. Using a *common* key in symmetric schemes makes symmetric cryptographic algorithms faster and more efficient for encrypting and decrypting large amounts of data. They are also more suitable for low-resource platforms such as wireless sensor nodes because they require less processing power and memory. However, the challenge with symmetric schemes is that the *common* key needs to be shared over an unsecured channel between two parties (sender and receiver), which makes it potentially vulnerable to attacks.

On the other hand, PKC uses two keys, public and private. The public key is widely available and can be used by anyone to encrypt original information/data, while the private key is kept secret by the recipient and is used to decrypt the data. This makes PKC schemes secure, especially for applications that require longer-term security or when the parties involved have no prior relationship or secure communication channel. However, public-key schemes are typically slower and require more processing power and memory than symmetric schemes.

The choice of the cryptographic scheme depends on the specific requirements of the application or platform, such as the level of security needed. PKC-based cryptographic schemes are beneficial for achieving longer-term security, and their security strength depends on solving prime factorization and discrete logarithm problems. In number theory, integer factorization decomposes a composite number into a product of a smaller integer. The process is prime factorization if the roots are restricted to prime numbers. A composite number is a positive integer formed by multiplying two smaller positive

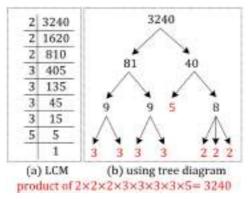

integers. In other words, it is a positive integer that has at least one divisor other than 1 and itself. Every positive integer is composite, prime, or unit, so the composite numbers are precisely those that are not prime and not a unit. For instance, integer 14 is a composite number because it is a product of the two smaller integers (i.e.,  $2 \times 7$ ). In contrast, the integers 2, 3, 5, and 7 are not composite numbers because they can divide only by 1 and themselves. Now, let us consider the following example to comprehend prime factorization. Take a prime P and let P be equal to 3240, and assume we need to find all prime roots/factors. The simplest way to do this is by finding the least common multiples (LCM), as factored in high school classes, and presented in Fig. 1 (left). The multiplication of the identified roots ensures the correctness of getting the original prime back. Note that the LCM method is effective only when the prime numbers are relatively small but for large primes, creating a tree diagram – as illustrated right side in Fig. 1 – is more beneficial.

Figure 1: Methods for calculating prime factorization.

For discrete logarithms, we need to fix a prime P. Let a, b be nonzero integers  $(mod \ P)$ . The problem of finding x such that  $a^x \equiv b \pmod{P}$  is called the discrete logarithm problem. Assume that n is the smallest integer such that  $a^n \equiv (mod \ P)$ . By assuming  $0 \leq x < n$ , we denote  $x = L_a(b)$  and call it the discrete logarithm of b with respect to  $a \pmod{P}$ . For example, let the prime P = 11, a = 2 and b = 9, then  $x = L_2(9) = 6$ .

Some open-source tools in the literature exist for factoring large primes and computing discrete logarithms. For example, an open-source CADO-NFS tool for integer factorization is available in [7], and it incorporates C/C++ implementations of the Number Field Sieve (NFS) algorithm [8] for factoring integers and computing discrete logarithms in finite fields. It is important to mention that not every integer is a prime, but for sufficiently large prime P, the literature demonstrates that the prime factorization and discrete logarithm problems are hard to solve on traditional computers and even on the fastest supercomputers because no efficient classical or non-quantum factorization algorithm is known.

The recent development in super-fast quantum computers [9, 10] raises issues in security and privacy. A quantum algorithm, named Shor's [11], provides a way to solve prime factorization and discrete logarithm problems exponentially faster than classical algorithms, making current PKC standards – Rivest, Shamir, and Adleman (RSA) [12] and elliptic curve cryptography (ECC) [13] – vulnerable to attacks by quantum computers. Therefore, two emerging directions such as quantum cryptography (QC)

and post-quantum cryptography (PQC) found in the literature to tackle these security concerns.

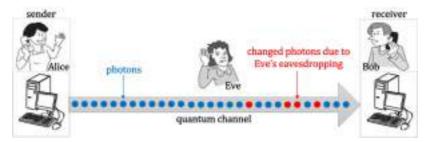

QC uses quantum mechanical properties to perform cryptographic tasks. At a very high level, the quantum cryptography model with the case of Alice, Bob, and Eve, is shown in Fig. 2. Alice and Bob want to send a secret to each other. Moreover, Alice sends Bob a series of polarized photons over a quantum channel (could be fiber optic cable), as shown in Fig. 2. If an eavesdropper, Eve, tries to listen in on the conversation, she must read each photon to read the secret. Then she must pass that photon on to Bob. By reading the photon, Eve alters the photon's quantum state, which introduces errors in the quantum key. This alerts Alice and Bob that someone is listening and the key has been compromised, so they discard it. Alice has to send Bob a new key that is not compromised, and then Bob can use that key to read the secret. The main advantage of quantum cryptography is that it allows the completion of many cryptographic tasks that are proven or presumed impossible using non-quantum communication. For instance, the data encoded by a quantum state is impossible to copy and modify. If someone tries to read the encoded data, the quantum state will be changed due to wave function collapse (no-cloning theorem [14]). This helps to detect eavesdropping in quantum key distribution.

Figure 2: Quantum cryptography model with the case of Alice, Bob, and Eve.

On the other hand, PQC uses mathematical-based problems for constructing quantum-resilient algorithms or protocols to protect communications against quantumcomputer attacks. Hence, the scientific community is constructing new reliable quantumresistant cryptographic protocols, and standardization bodies and commercial organizations are also considering PQC alternatives. For example, in January 2020, the Chinese Association for Cryptologic Research (CACR) finished its PQC-standardization contest and selected LAC [15] as a winner for key establishment/agreement. Another example is an ongoing contest – initiated by the American National Institute of Standards and Technology (NIST) in 2017 – for post-quantum public-key cryptography standards. After the third round in 2022, NIST selected CRYSTALS-Kyber [16] and CRYSTALS-Dilithium [17] and stimulated the competition process in round four to investigate other protocols/algorithms. Note that quantum computers are still in their early stages of development, and only the big organizations like Google, IBM, etc., will have quantum computers soon; regular users wouldn't, and it may take a couple of years to come into the market. But some quantum computers have already been developed. In 2019, Google claimed to have the Sycamore – a 53 quantum bit (qubit) - quantum computer [9], which takes 200 seconds to sample one instance of a quantum circuit. The equivalent task on a supercomputer would take approximately 10,000 years. In 2021, IBM developed a 127 qubits processor, named Eagle [10]. According to [18], the Eagle chip is a step towards IBM's goal of creating a 433-qubit quantum processor

next year, followed by one with 1,121 qubits, named *Condor*, by 2023. Therefore, quantum-resistant cryptographic schemes are mandated to protect future and present communications.

The security strength of the NIST candidates for PQC standardization relies on several mathematical problems, including code, multivariate, isogeny, lattice, and hash. Amongst these, the lattice-based schemes are the most promising due to their computational efficiency, strong security assurance, and support for different applications; so from onward, this thesis discusses only lattice-based cryptography. Indeed, lattice-based cryptography has become a popular area of research in the last decade due to the introduction of the Learning With Errors (LWE) [19] and Learning With Rounding (LWR) [20] problems. The NIST selection of CRYSTALS-Kyber and CRYSTALS-Dilithium algorithms relies on LWE-based lattice cryptography, which confirms the increasing interest in this field. SABER [21], an LWR-based scheme, remained part of the NIST competition until round three [22] and is investigated as a case study in this thesis.

Despite the level of security needed, the choice of the cryptographic scheme (also) relies on the specific requirements of the application or platform, such as the available resources and the speed of encryption and decryption required. The applications related to the internet of things and wireless sensor nodes demand area- and power-constrained accelerators for cryptographic computations. High-speed cryptographic computations are always required for many applications, including wireless, telecom, cloud, data centers, enterprise systems, and network-related devices. For these applications, 8920 and 8955 families of Intel chipsets can process 5k, and 40k RSA decryption operations in one-second [23]. IBM 4769 hardware security module offers security services like key exchange and signature generation/verification using ECC and RSA standards [24]. Although these distinctive chips offer thousands of operations per second, they might become compromised since the security of ECC and RSA can be broken using Shor's algorithm [11] on a quantum computer. Hence, high-speed quantum-resistant cryptographic hardware accelerators are mandated to supersede ECC- and RSA-based devices.

The most commonly used platforms for implementing hardware accelerators are field programmable gate array (FPGA) and application-specific integrated circuit (ASIC). FPGAs are programmable hardware devices that can be configured and reconfigured to perform various tasks, including PQC algorithm acceleration. It offers several advantages: flexibility, reusability, and low development cost, and it can also be used to accelerate multiple PQC algorithms, making them a versatile choice. ASIC, on the other hand, are custom-built integrated circuits that are optimized for specific tasks or applications and offer higher performance and power efficiency than FPGA. However, ASICs are expensive to design and manufacture and are not reconfigurable. The choice between FPGA and ASIC for implementing PQC hardware accelerators will depend on factors such as the specific PQC algorithm(s) being accelerated, the required performance, and the available resources and budget. Keeping these factors in mind, some existing FPGA and ASIC hardware accelerators of quantum-resistant protocols (such as CRYSTALS-Kyber, CRYSTALS-Dilithium, and SABER) are implemented in [25, 26, 27, 28, 29, 30, 31, 32, 33, 34, 35, 36]. These implementations only provide the hardware demonstrations without the design optimizations for specific to certain parameters (such as low area, low power, high speed, etc.), hence posing a question: how to further maximize the performance of PQC algorithms when demonstrated as hardware accelerators?. This is the problem that this thesis explores.

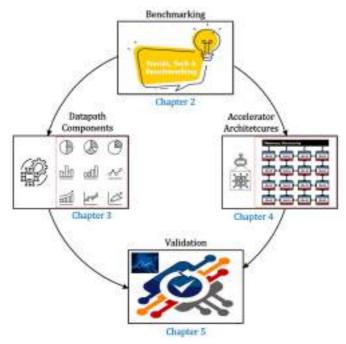

Figure 3: Structure of the thesis.

## 1.1 Novelty, Contributions & Summary of the Thesis

The thesis focuses on lattice-based PQC schemes and their performance improvement on the ASIC platform. Fig. 3 presents the overall structure of the thesis. Each chapter is a novel contribution to this thesis, and the corresponding details are as follows.

- Chapter 2 This chapter gives a comprehensive overview of the concepts related to lattice-based PQC. Also, this chapter analyzes the building blocks of several lattice-based post-quantum algorithms, estimates their area and power on the ASIC platform, and concludes by selecting SABER [21] as the algorithm for hardware demonstrations and optimizations. Moreover, this chapter also describes the mathematical background for understanding the SABER algorithm and provides implementation platforms trade-off.

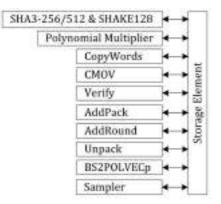

- Chapter 3 The design of cryptographic hardware accelerators depends on polynomial arithmetic (addition, multiplication, inversion, sampling, hash, etc.) and logical operations in their datapath. However, polynomial multiplication is a computationally expensive operation in cryptographic schemes. Mostly the implementations of polynomial multipliers are specific to operands length and are not open-source for free use to everyone. Therefore, for the first time, I developed an open-source generator/tool for multiplying large integer polynomials to be used in conventional PKC algorithms (such as RSA and ECC) and PQC schemes. This chapter describes the structure/architecture of the developed multiplier generator tool. It offers flexibility, digitizing, pipelining, and also generates scripts for different ASIC synthesis tools, such as Cadence Genus and Design Compiler (DC) by Synopsis. Different figure-of-merits in Power-Area-Performance (PAP)

are defined to evaluate different polynomial multiplication architectures generated by the developed multiplier generator.

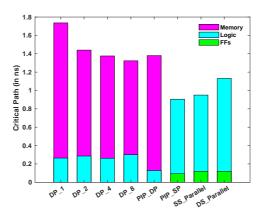

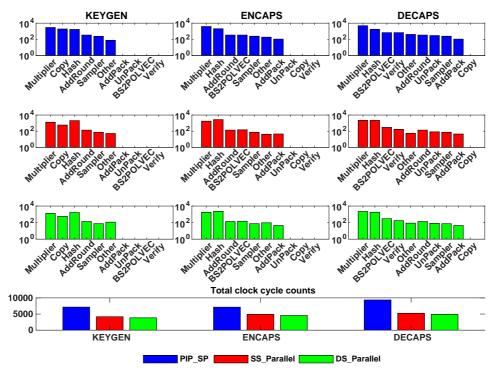

- Chapter 4 The focus of this chapter is to provide a design space exploration (DSE) process of SABER for optimizing circuit frequency specific to the ASIC platform. The DSE process is initiated by setting a baseline architecture of SABER. Then, several memory types are utilized to evaluate the circuit frequency. Pipelining is incorporated to reduce the critical path of the SABER design. Parallel architectures are also proposed and implemented to reduce the clock cycle requirements for cryptographic computations, eventually improving the performance.

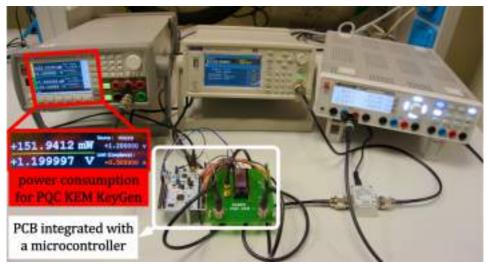

- Chapter 5 In this chapter, a high-speed SABER chip is designed and fabricated on a 65nm process technology. It is important to mention that designing a Printed Circuit Board (PCB) is trivial for verification purposes. Therefore, I mount the fabricated chip on a PCB and interface it with a microcontroller, which helps to provide/collect inputs/outputs to/from the chip. All these details are described in this chapter. The fabricated chip is the fastest silicon demonstrated amongst state-of-the-art SABER chips regarding operating frequency.

- Chapter 6 This chapter concludes the thesis. It provides future directions which indicate that the techniques studied in this thesis can be applied to other PQC algorithms, including CRYSTALS-Kyber and CRYSTALS-Dilithium, to improve their computation speed.

# 2 Background

This chapter describes the concepts related to lattice problems and the building blocks (i.e., multipliers, hash, samplers, etc.) needed for constructing lattice-based PQC algorithms in Sections 2.1 and 2.2, respectively. The SABER PQC protocol is described in Section 2.3. The existing hardware accelerators of lattice-based PQC algorithms are described in Section 2.4.

## 2.1 Lattice-Based Post-Quantum Cryptography

This section describes an overview of the hard problems defined over lattices. Such problems are a class of optimization problems and their conjectured intractability is the foundation of lattice-based public-key cryptography schemes [37]. Lattice problems have been studied for centuries and are considered hard to be solved. In 1996, Ajtai proposed the first significant public-key scheme using lattices in [38], which offered provable security, resistance to quantum computers, and worst-case hardness. Before defining the lattice problems, it is essential to define the elements (lattice, vector, and basis) on which the lattice problems depend.

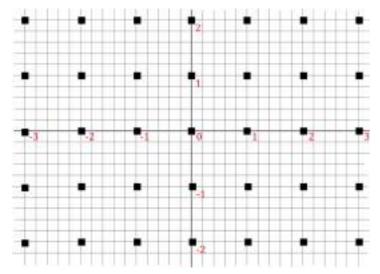

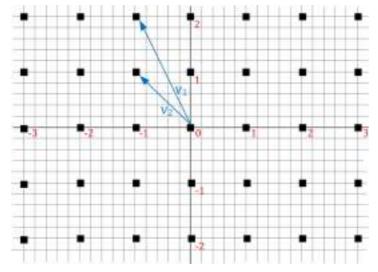

Lattice. A lattice L ∈ ℝ<sup>m</sup> is a set of points in m-dimensional space with a periodic structure. An example of a two-dimensional lattice is shown in Fig. 4, where each box (filled with a black color) specifies the lattice point.

Figure 4: An example of a two-dimensional lattice over a set of all real numbers.

Vector. A vector represents a quantity with magnitude (distance) and direction. Vectors can have different dimensions, however, the most intuitive is in twodimensional or three-dimensional space. Below, Eq. 1 and Eq. 2 show the two-dimensional and three-dimensional vectors with their coordinates/elements.

$$\vec{v_1} = (2,1) \& \vec{v_2} = (2,8) \in \mathbb{R}^2$$

(1)

$$\vec{v_1} = (2,1,4) \& \vec{v_2} = (2,8,5) \in \mathbb{R}^3$$

(2)

**Basis.** A basis is a collection of vectors to produce a point in a given space.

**Definition 2.1.1.** Lattice [39]. Let v be a set of n linearly independent vectors  $v_0, v_1, \ldots, v_{n-1} \in \mathbb{R}^m$ . The lattice  $\mathcal{L}$  is the set of linear combinations of the vectors with coefficients in  $\mathbb{Z}$ , as shown in Eq. 3.

$$\mathcal{L} = \{a_0.v_0, +\dots + a_{n-1}.v_{n-1}\} = \sum_{i=0}^{n-1} a_i.v_i \in \mathbb{Z}$$

(3)

In Eq. 3, v is a basis of  $\mathcal{L}$ , n specifies its rank and m determines its dimension. The lattice is a full-rank if n = m. Fig. 5 presents an example of a two-dimensional lattice with a basis of vectors  $v_1$  and  $v_2$ . Any point in the lattice can be reached by an integer combination of vectors  $v_1$  and  $v_2$ .

Figure 5: A two-dimensional lattice with two basis vectors  $v_1$  and  $v_2$ . The coordinates of  $v_1$  and  $v_2$  are (-1, 2) and (-1, 1), respectively.

Lattice approximate problems. The shortest vector problem (SVP) and close vector problem (CVP) are two of the most important lattice approximate problems that play a significant role in the security of lattice-based cryptography [37]. These problems are presumed to be difficult to solve, which makes lattice-based cryptography secure. Therefore, the formal construction of SVP and CVP problems is described below.

**Definition 2.1.2.** SVP [40]. The SVP is finding the shortest non-zero vector in a lattice  $\mathcal{L}$ , which is defined by n linearly independent and randomly chosen basis vectors. In other words, find a non-zero vector v in a lattice  $\mathcal{L}$  such that  $||v|| = \lambda_1(\mathcal{L})$ , where ||v|| is the Euclidean norm of the length of a vector v in  $\mathcal{L}$ ,  $\lambda_1$  is the shortest vector.

It shows in [38] that the SVP with Euclidean norm is NP-hard for randomized reductions. The SVP<sub> $\gamma$ </sub> is an  $\gamma$ -approximation version of the SVP where one has to find a vector  $v_{\gamma}$  in  $\mathcal{L}$  such that  $||v_{\gamma}|| \leq \gamma \lambda_1(\mathcal{L})$ .

**Definition 2.1.3.** CVP [39]. Given a target vector  $t \in \mathbb{R}^m$  that is not necessarily in  $\mathcal{L}$ , find a vector  $v \in \mathcal{L}$  that is closest to t. In other words, finding a vector  $v \in \mathcal{L}$  reduces the Euclidean norm || t - v ||.

Like SVP<sub> $\gamma$ </sub>, CVP<sub> $\gamma$ </sub> is an  $\gamma$ -approximation of the CVP where one has to find a vector  $v_{\gamma}$  such that  $|| t - v_{\gamma} || \le || t - v ||$ . Note that the CVP<sub> $\gamma$ </sub> is the generalization of the SVP<sub> $\gamma$ </sub>. Thus, CVP is also known to be NP-hard [38].

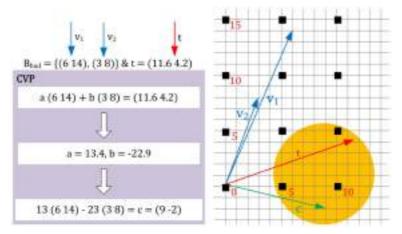

The SVP or CVP or their approximate versions (SVP $_{\gamma}$  and CVP $_{\gamma}$ ) can be solved easily when a basis in a lattice consists of either orthogonal or near orthogonal vectors, also when short vectors are known. A set of orthogonal vectors describes a good basis. Let us do examples to see the effect of *bad* and *good* basis in lattice-based cryptography. The following examples are taken from [41]. Given a basis  $B_{bad} = \{(6 \ 14), (3 \ 8)\}$ consisting of two vectors  $v_1$  and  $v_2$  with coordinates (6 14) and (3 8). Notice that  $v_1$  and  $v_2$  are not orthogonal to each other. Also, a target vector t = (11.6 4.2) is given. Then the approximation problem asks for the nearest point of a given lattice to challenge the target point. The left portion in Fig. 6 describes the whole scenario, where a system of the equations for the given basis and target t must be solved to find the values of a and b. As seen in Fig. 6, the calculated values for a and b are real numbers (i.e., 13.4 and -22.9); these values cannot be used to calculate the lattice point (c), so the real values must be rounded up or down to get the integers (the closest value of 13.4 is 13 and -22.9 is -23) - this is the lattice approximation. After that, the values of a and b need to be used in the identical system of equations to calculate the lattice point. As shown green vector in Fig. 6, the calculated lattice point is (9-2) and is far from the red vector, which is a target point  $t = (11.6 \ 4.2)$ . The graphical visualization of the complete scenario is illustrated in the right part of Fig. 6, where the orange circle highlights that the target and calculated points are far from each other.

Figure 6: Example of a *bad* basis where the orange circle focuses on the target and calculated points far from each other. The purple portion solves the lattices for CVP.

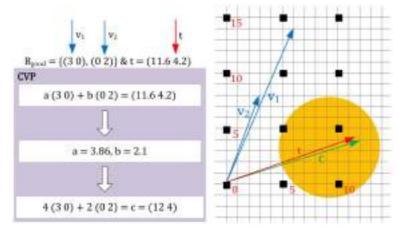

Similarly, let us consider a basis  $B_{good} = \{(3 \ 0), (0 \ 2)\}$  consisting of two vectors  $v_1$  and  $v_2$  with coordinates  $(3 \ 0)$  and  $(0 \ 2)$ . Here, notice that the  $v_1$  and  $v_2$  are orthogonal. The same target vector  $t = (11.6 \ 4.2)$  is considered. The approximation problem asks for the closest point of a given lattice to challenge the target point. The left portion in Fig. 7 describes the whole scenario, where a system of equations for the given basis and target t must be solved to find the values of a and b. As seen in Fig. 7, the calculated values for a and b are real numbers (i.e., 3.86 and 2.1); these values cannot be used to calculate the lattice point c, so the real values must be rounded up or down to get the integers (the closest value of 3.86 is 4 and 2.1 is 2) – this is the lattice approximation.

After that, the values of a and b need to be used in the identical system of equations to calculate the lattice point. As shown by the green vector in Fig. 7, the calculated lattice point is (12 4) and is closest to the given target point t = (11.6 4.2). The graphical visualization of the complete scenario is illustrated in the right part of Fig. 7, where the orange circle highlights that the target and calculated points are closer to each other.

Figure 7: Example of a *good* basis where the orange circle focuses on the target and calculated points closer to each other. The purple portion solves the lattices for CVP.

Consequently, lattice reduction algorithms in the literature aim to build a *good* basis from any given basis for a lattice. For example, the LLL algorithm [42] outputs an LLL-reduced basis in a polynomial time but with the approximation factor of  $W^n$ , where W is a small constant. Hence, the LLL algorithm is effective in scenarios where the dimension n of the lattice is very small. The algorithms that achieve close approximation can run in approximation time. Examples of such algorithms are AKS [43], and BKZ [44]. The inability of the lattice reduction algorithms to find a good basis in polynomial time is used as the construction for lattice-based cryptography schemes.

**LWE Problem.** As reported earlier in this section, Ajtai described the first latticebased public-key scheme in 1990 [38]. Later, in 2005, Regev [19] introduced a new lattice problem named LWE. Since its introduction, the LWE problem has become very popular for constructing various schemes such as public-key encryption, key exchange, digital signature generation/verification, and even homomorphic encryption schemes [37]. The LWE problem can be defined by a lattice with dimension n, an integer modulus q, and an error distribution  $\chi$  over integers  $\mathbb{Z}$ . A secret vector  $\mathbf{s}$  of dimension n is generated by choosing its coefficients uniformly in an n-dimensional ring  $\mathbb{Z}_q^n$ . Generate random vectors  $\mathbf{a}_i$  by uniformly and error terms  $e_i$  from the error distribution  $\chi$ . After that compute  $b_i = \langle \mathbf{a}_i, \mathbf{s} \rangle + e_i \in \mathbb{Z}_q$ . Then the LWE distribution is denoted as  $A_s, \chi$  over  $\mathbb{Z}_q^n \times \mathbb{Z}_q$  and is the set of tuples  $(a_i, b_i)$ . The lower bold characters show the vectors of dimension n. The decision and search are the two variants of LWE, defined below.

**Definition 2.1.4.** decision LWE problem [45]. Solving the decision LWE problem is to distinguish with non-negligible advantage between the samples drawn from LWE distribution  $A_s, \chi$  and the same number of samples drawn uniformly from  $\mathbb{Z}_q^n \times \mathbb{Z}_q$ .

**Definition 2.1.5.** search LWE problem [45]. Find a secret **s** when a polynomial number of samples from the LWE distribution  $A_s, \chi$  is given.

Note that the cryptosystems constructed on the security hardness of the original LWE

problem are slow because they need computations on larger matrices with coefficients from  $\mathbb{Z}_q$ . Hence, in literature, another computationally efficient variant of the LWE problem is defined over polynomial rings, called the ring-LWE problem [46].

Lyubashevsky, Peikert, and Regev initially introduced the ring-LWE problem [47]. Ring-LWE uses a particular class of lattices named "ideal lattices" to attain computational efficiency and reduce the key size. Therefore, the ring LWE problem is defined over a polynomial ring  $R_q = \mathbb{Z}_q[x]/\langle f \rangle$ , where  $\langle f \rangle$  is an irreducible polynomial of degree n and coefficients of  $\langle f \rangle$  contain modulus q. The problem is defined as follows: Sample a secret polynomial s(x), and error polynomials  $e_i(x) \in R_q$  with coefficients from  $\chi$ . Next, generate polynomials  $a_i(x)$  with coefficients chosen uniformly from  $\mathbb{Z}_q$ . Compute  $b_i(x) = a_i(x).s(x) + e_i(x) \in R_q$ . The ring-LWE distribution is the set of polynomial tuples  $(a_i(x), b_i(x))$ . As mentioned,  $e_i$  specifies the error polynomials with coefficients sampled from an n-dimensional error distribution  $\chi$ . It is essential to highlight that the error distribution is a discrete Gaussian distribution is the product of n independent discrete Gaussians. Note that, in general,  $\chi$  is more complicated to compute. One can form s by sampling the coefficients from  $\chi$  rather than uniformly without any security implications [47].

**Definition 2.1.6.** decision ring-LWE problem [47]. Distinguish between the samples  $(a_i(x), b_i(x))$  drawn from the ring-LWE distribution and the same number of samples generated by choosing the coefficients uniformly.

**Definition 2.1.7.** search ring-LWE problem [47]. Find a secret polynomial s(x) given a polynomial number of samples constructed from the ring-LWE distribution.

Instead of the ring-LWE, another variant of LWE schemes is module-LWE. In contrast, ring-LWE uses polynomial ring elements, whereas module-LWR employs matrices of ring elements to define the problem. As summarized, there exist two cases. In the first case, when f specifies a cyclotomic polynomial [47], then the difficulty of the search ring-LWE problem is roughly equivalent to finding a short vector in an ideal lattice (composed of polynomials from R). A cyclotomic polynomial is a unique irreducible polynomial. In the second case, for the LWE problem, the security strength is related to solving the NP-hard  $SVP_{\gamma}$  over general lattices. These two cases are presumed to be equally difficult because no proof is known (to date) to show equivalence between the  $SVP_{\gamma}$  for general and ideal lattices. The computational efficiency using the ring-LWE problem is obtained at the cost of the above security assumption. The cryptographic schemes constructed on the ring-LWE problem are fast due to simple polynomial arithmetic [46].

**LWR Problem.** LWR is a variant of the LWE problem where random errors are replaced with deterministic rounding. Initially, the LWR problem was introduced in [48], and later, it was revisited in [49]. The LWR problem concerns the cryptographic properties of the function  $f_s: \mathbb{Z}_q^n \to \mathbb{Z}_p$ , given by  $f_s(x) = \lfloor \langle x, s \rangle \rceil_p = \lfloor (P/q) . \langle x, s \rangle \rceil$ . Here,  $s \in \mathbb{Z}_q^n$  and is a secret key. The term  $\langle x, s \rangle$  determines the inner product of x and  $s \mod q$ . The  $\lfloor . \rceil$  denotes the closest integer. For mathematical derivations and more details, readers are referred to [38, 19] for the LWE problem and [48, 49, 50] for the LWR problem.

### 2.2 Building-Blocks for Lattice-Based Crypto Systems

This section deals with the building blocks of lattice-based PQC algorithms submitted to NIST for standardization. Currently, the NIST standardization process is in round four. I have started investigating the lattice-based PQC candidates submitted to NIST for standardization in 2020. At that time, the NIST competition was in round two. All

Table 1: Multiplication and hash methods for different PQC algorithms. These methods are obtained from their reference implementations, available at NIST sites [61] (after round-2) and [22] (after round-3).

| PQC Algorithms          | Multiplication Methods  | Hash Methods                   |

|-------------------------|-------------------------|--------------------------------|

| qTesla [51]             | NTT and SBM             | SHAKE-256 and cSHAKE-128/256   |

| CRYSTALS-Dilithium [17] | NTT                     | SHAKE-128/256                  |

| NTRU-Prime [52]         | SBM                     | SHA2-512                       |

| NewHope [53]            | NTT                     | SHAKE-128/256                  |

| ThreeBears [54]         | Karatsuba               | cSHAKE-256                     |

| LAC [55]                | SBM                     | -                              |

| Round5 [56]             | SBM                     | cSHAKE-256 and AES-256         |

| CRYSTALS-Kyber [16]     | NTT                     | SHA3-256/512 and SHAKE-128/256 |

| NTRU [57]               | Karatsuba and Toom-Cook | SHA3-256                       |

| FrodoKEM [58]           | SBM                     | SHAKE-128/256                  |

| Falcon [59]             | SBM                     | SHAKE-256                      |

| SABER [21]              | Karatsuba and Toom-Cook | SHAKE-128, SHA3-256/512        |

Note that the multiplication and hash methods in columns two and three have been considered from the reference C/C++ codes of PQC algorithms that were submitted to NIST for evaluation.

the lattice-based PQC algorithms that participated in the second and third rounds of the NIST contest are qTesla [51], CRYSTALS-Dilithium [17], NTRU-Prime [52], NewHope [53], ThreeBears [54], LAC [55], Round5 [56], CRYSTALS-Kyber [16], NTRU [57], FrodoKEM [58], Falcon [59], and SABER [21]. These PQC algorithms require various building blocks depending on the construction of the cryptographic protocol to perform cryptographic tasks. However, the polynomial multiplication and hash are the most critical operations to compute [60]. Table 1 lists different polynomial multiplication and hash operations, and the text below provides the implementation details of these multiplication and hash methods.

Polynomial multiplication involves multiplying two polynomials (i.e., a and b) and obtaining a resultant polynomial (i.e., c). The degree of the resulting polynomial is the sum of the degrees of the two input polynomials. The polynomial multipliers can be categorized into serial and parallel designs. In the case of bit-serial multipliers such as schoolbook (SBM) and Booth multipliers, the multiplication of polynomials is performed bit-by-bit, resulting in a sequence of partial products. These partial products are then added together to obtain the resultant polynomial. On the other hand, bit-parallel multipliers split the input polynomials into multiple parts and perform the multiplication of these parts in parallel. The inner product of the split portions is computed, and the resulting polynomial is generated using addition and subtraction operations. The 2-way Karatsuba multiplier is a famous bit-parallel multiplier that splits the input polynomials into two equal parts and uses three multiplications along with some additions and subtractions to compute the inner product. The 3-way and 4-way Toom-Cook multipliers split the input polynomials into three and four equal parts, respectively, and use a more complex algorithm to compute the inner product. Overall, bit-parallel multipliers are faster and more efficient than bit-serial multipliers, especially for larger input sizes. However, they also require more hardware resources and may not be practical for small input sizes.

**SBM multiplier.** SBM is the simplest way to multiply two input polynomials  $a(x) \times b(x)$ , as shown in Eq. 4. The resultant polynomial c(x) is generated by performing bit-by-bit operations. Algorithm 1 shows the number of steps required to perform polynomial multiplication for the SBM multiplier, where polynomial a is multiplied with the shifted polynomial b to produce the resultant polynomial c. The latency associated with an SBM multiplier is  $\lceil m \rceil$  clock cycles, whereas the operations to be computed

are (m-1) additions and m multiplications (shifts).

$$c(x) = \sum_{i=0}^{m-1} \sum_{j=0}^{m-1} a_i b_j x^{i+j}$$

(4)

| Algorithm 1: Traditional SBM multiplication                    |  |

|----------------------------------------------------------------|--|

| <b>Input:</b> a and b $(m-bit \ polynomial \ integers)$        |  |

| <b>Output:</b> $c \leftarrow a \times b$                       |  |

| 1 for (j from 0 to $m-1$ ) do                                  |  |

| 2   if $b_j = 1$ then                                          |  |

| 2   if $b_j = 1$ then<br>3   $c \leftarrow c + (a \times 2^j)$ |  |

|                                                                |  |

| 4 return c                                                     |  |

**Booth multiplier.** Similar to the SBM, the traditional Booth multiplier exploits add, subtract, and shift operations. Yet, unlike the SBM, it does not look at a bit at a time [62]. It observes two bits at a time and reduces the required addition and subtraction operations, ultimately reducing the multiplier's latency. The traditional Booth multiplication method is presented in Algorithm 2, where A keeps the generated partial product (initialized with 0). The  $\overline{b}$  shows the extended polynomial with the addition of a dummy 0-bit next to the least significant bit of the multiplier (b). It computes multiplication by inspecting the least significant two bits of the multiplier to match these four cases: 00, 01, 10, and 11. When the inspected bits are either 00 or 11, it means to do nothing or remain unchanged. For the remaining two cases, the multiplicand may be added (line 5) or subtracted (line 8) from the partial product (A). The  $shift\_right\_add$  function of lines 6 and 9 in Algorithm 2 determines the multiplication of multiplicand by 2 with shift and add operations. For two operands of length m, Algorithm 2 takes m/2 clock cycles. Follow [62] for additional details.

#### Algorithm 2: Booth Multiplication

```

Input: a and b (m - bit polynomial integers)

Output: c \leftarrow a \times b

1 A \leftarrow 0 \ (m-bit \ temporary \ integer)

2 \overline{\mathbf{b}} \leftarrow \{b, 0\}

3 for (j from 0 to m-1) do

if \overline{\mathbf{b}}_{i+1} \times \overline{\mathbf{b}}_i = 01 then

4

A \leftarrow A + a

5

c \leftarrow shift\_right\_add(A, \overline{\mathbf{b}}_{j+1}, \overline{\mathbf{b}}_{j})

6

if \overline{\mathbf{b}}_{j+1} \times \overline{\mathbf{b}}_j = 10 then A \leftarrow A - a

7

8

c \leftarrow shift\_right\_add(A, \overline{b}_{j+1}, \overline{b}_{j})

9

10 return c

```

**Karatsuba multiplier.** A generalized Karatsuba multiplier contains l number of levels to perform polynomial multiplication, where l depends on the user or designer to choose. For example, let us assume we have two input polynomials,  $z_1$  and  $z_2$ . At the first level,  $z_1$  and  $z_2$  are divided into two smaller polynomials,  $\frac{z_1}{2}$  and  $\frac{z_2}{2}$ . At the

second level, each split polynomial is further divided into two other polynomials, i.e.,  $\frac{z_1}{4}$  and  $\frac{z_2}{4}$ . The process of splitting polynomial repeats until the value l is reached. After splitting the input polynomials, the inner product can be computed, which is achieved using three inner multiplications, a few additions, and shift operations on small(er) operands. Eventually, the resulting polynomial is generated with the multiplications starting from the smaller polynomials to the larger one in a reverse order (meaning multiplications start from  $\frac{z_1}{4}$  and  $\frac{z_2}{4}$  to  $z_1$  and  $z_2$ ).

From Eq. 4, the split polynomial is derived in Eq. 5 where *n* shows the polynomial splits and *k* determines the index of the split polynomial. For a specific 2-way Karatsuba multiplier<sup>1</sup>, the expanded version of Eq. 5 is shown in Eq. 6. It requires four multiplications for the execution of inner products (one to achieve the resulting polynomial  $c_1(x)$ , two multiplications for the execution of  $c_2(x)$ , and eventually one for the execution of  $c_0(x)$ ). As presented in Eq. 7, the Karatsuba observation was to compute  $c_2(x)$  with only one multiplication instead of two. The addition of inner products is required to generate the resultant polynomial c(x), as presented in Eq. 8. Algorithm 3 provides the number of steps for the 2-way Karatsuba polynomial multiplication method. As the name implies, function add\_shift in line 8 of Algorithm 3 applies the shift and add operations over the polynomials given in parentheses. In total,  $\lceil \frac{m}{2} \rceil$  clock cycles are needed to implement one *m*-bit polynomial multiplication.

$$c(x) = \underbrace{\left(\sum_{i=\frac{k\times m}{n}}^{m-1} a_{\mathbf{k}}(x) + \ldots + \sum_{i=0}^{\frac{k\times m}{n}-1} a_{\mathbf{0}}(x)\right)}_{split \, polynomial \, a(x)} \times \underbrace{\left(\sum_{i=\frac{k\times m}{n}}^{m-1} b_{\mathbf{k}}(x) + \ldots + \sum_{i=0}^{\frac{k\times m}{n}-1} b_{\mathbf{0}}(x)\right)}_{split \, polynomial \, b(x)} \tag{5}$$

$$c(x) = \underbrace{a_1(x)b_1(x)}_{c_1(x)} + \underbrace{a_1(x)b_0(x) + a_0(x)b_1(x)}_{c_2(x)} + \underbrace{a_0(x)b_0(x)}_{c_0(x)}$$

(6)

$$c_2(x) = (a_1(x) + a_0(x)) \times (b_1(x) + b_0(x)) - c_1(x) - c_0(x)$$

(7)

$$c(x) = c_0(x) + c_1(x) + c_2(x)$$

(8)

#### Algorithm 3: 2-way Karatsuba Multiplication

(

Input: a and b  $(m-bit \ polynomial \ integers)$ Output:  $c \leftarrow a \times b$  $[b_1, b_0, a_1, a_0] \leftarrow \frac{[a, b]}{2}$  $c_0 \leftarrow a_0 \times b_1$  $c_1 \leftarrow a_1 \times b_1$  $c_{01} \leftarrow a_1 + a_0$  $c_{10} \leftarrow b_1 + b_0$  $c_2 \leftarrow c_{10} \times c_{01} - c_1 - c_0$ 7 for (j from 0 to  $\frac{m-1}{2}$ ) do  $\lfloor c \leftarrow c_0 + add\_shift(c_1, c_2)$ 9 return c

**Toom-Cook multiplier.** The Toom-Cook multiplication method is the advanced and extended form of Karatsuba multiplication. The difference is in dividing input

<sup>&</sup>lt;sup>1</sup>2-way Karatsuba means that the splitting of input polynomials for Karatsuba multiplication is applied only once.

polynomials into 3 and 4 parts instead of 2 (as in 2-way Karatsuba). With index k of the split input polynomials, the values for n = 3 and n = 4 in Eq. 5 determine the equations of 3-way and 4-way Toom-Cook multipliers. The expanded version of Eq. 5 produces nine and sixteen inner multiplications for 3-way and 4-way Toom-Cook multipliers, respectively. Using a process identical to the 2-way Karatsuba, the required nine and sixteen inner multiplications can be reduced to five and seven. The equations for variants of the Toom-Cook multiplier are not shown as it requires an identical procedure to the 2-way Karatsuba. However, Algorithm 4 presents a complete understanding of the Took-Coom multiplication method when the split input polynomials are three smaller polynomials. As the name implies, function  $add\_shift$  in line 8 of Algorithm 4 applies the shift and add operations over the polynomials given in parentheses. In total,  $\lceil \frac{m}{3} \rceil$  and  $\lceil \frac{m}{4} \rceil$  clock cycles are required to execute one m-bit polynomial multiplication.

#### Algorithm 4: 3-way Toom-Cook Multiplier Input: a and b $(m - bit \ polynomial \ integers)$ Output: $c \leftarrow a \times b$ 1 $[b_2, b_1, b_0, a_2, a_1, a_0] \leftarrow \frac{[a, b]}{3}$ 2 $c_0 \leftarrow a_0 \times b_0$ 3 $c_1 \leftarrow a_0 \times b_1 + a_1 \times b_0$ 4 $c_2 \leftarrow a_0 \times b_2 + a_1 \times b_1 + a_2 \times b_0$ 5 $c_3 \leftarrow a_1 \times b_2 + a_2 \times b_1$ 6 $c_4 \leftarrow a_2 \times b_2$ 7 for (j from 0 to $\frac{m-1}{3}$ ) do 8 $\lfloor c \leftarrow c_0 + add\_shift(c_1, c_2, c_3, c_4)$ 9 return c

**Multipliers based on Number Theoretic Transformation (NTT).** The NTTbased polynomial multiplication is an efficient way to multiply two polynomials over ring  $\mathbb{Z}_q[X]/\langle X^n+1\rangle$ , where  $\mathbb{Z}_q[X]/\langle X^n+1\rangle$  represent the polynomial ring reduced with cyclotomic polynomial  $(X^n+1)$  over  $\mathbb{Z}_q[X]$ . It is a generalization of the Fast Fourier Transform (FFT). Let we have a polynomial f with degree n, where  $f = \sum_{i=0}^{n-1} f_i X^i$ and  $f_i \in \mathbb{Z}_q$  and  $\omega_n$  be the n-th primitive root of unity such that  $\omega_n^n = 1 \mod q$ . Then the forward NTT can be defined by  $\hat{f} = NTT(f)$ , such that  $\hat{f}_i = \sum_{j=0}^{n-1} f_j \omega_n^{ij}$ mod q. Similarly, the inverse NTT can be computed by  $f = INTT(\hat{f})$ , such that  $f_i = n^{-1} \sum_{j=0}^{n-1} \hat{f}_j \omega_n^{-ij} \mod q$ . Based on these definitions, an NTT-based polynomial multiplication between a and b can be performed such that  $a.b = INTT(NTT(a) \circ NTT(b))$ .

The NTT-based multiplication computes on convolution, which transforms the input polynomials of length n to 2n with zeros padding, resulting in more computation time. Therefore, to avoid applying the NTT of length 2n with n zero padding of inputs, a negative wrapped convolution (NWC) [63] method is introduced at the cost of preprocessing of NTT and post-processing of INTT. Let us say  $\psi = \sqrt{\omega_n}$ ; it is a primitive 2n-th root of unity. The pre-processing cost includes the multiplication between the coefficients of the input polynomials and  $\psi^i$ . In contrast, the post-processing cost includes the multiplication between the coefficients of the output polynomials and  $\psi^{-i}$ .

The CooleyTukey (CT) and Gentleman-Sande (GS) butterfly configurations are the most frequently employed in literature on NTT-based implementations. Using these configurations reduces the bit-reverse operation in NTT, which is the bit-wise reversal

of the binary representation of the coefficient index. For more insight details at the algorithmic level, interested readers are referred to [64], and to follow some recent NTT-based hardware accelerators, readers are referred to [65, 66, 67].

The last column of Table 1 shows the hash methods implemented in different PQC algorithms for various purposes, such as binomial sampling. The PQC schemes of column one of Table 1 contributed in rounds two and three of the NIST competition process and mainly depended on variants of the SHA2, SHA3, and SHAKE-128/256 hash functions. This thesis is not describing the inner structures of these hash functions; however, the only objective is to highlight the complexity of the PQC schemes when realized as hardware accelerators. NIST standardizes the most recent SHA3 and its variants in [68] and is mainly used in all PQC schemes of Table 1, including the NIST selected CRYSTALS-Kyber and CRYSTALS-Dilithium algorithms to be standardized in the near future.

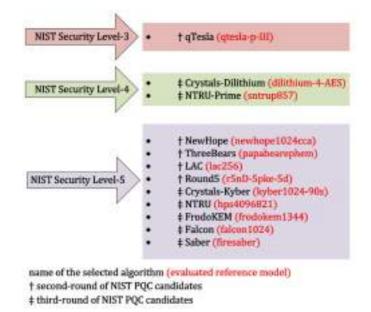

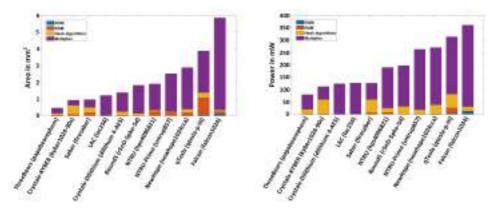

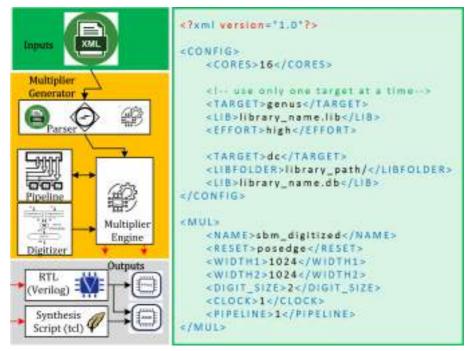

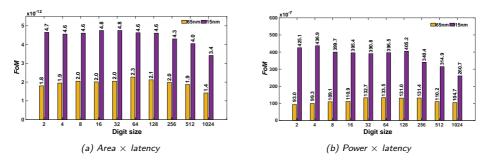

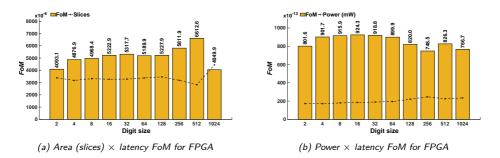

Also, the computation time of polynomial multiplications and hash operations of the PQC algorithms depends on their security parameters. NIST has defined five security levels (1 to 5) for investigating PQC algorithms. Security levels 1, 3, and 5 are equivalent to AES-128, AES-192, and AES-256 bit key search. The remaining security levels (2 and 4) are equivalent to SHA-256/SHA3-256 and SHA-384/SHA3-384 bit collision search. Implementing all security levels in one hardware design requires large memory utilization. In other words, despite the polynomial multiplications and hash operations, large memory utilization is also the key characteristic of the PQC algorithms when demonstrated as hardware accelerators. Therefore, in [69], I have evaluated the memory, hash, and multiplier building blocks of PQC algorithms of Table 1, where I have targeted the highest security parameters shown in Fig. 8. The detailed outcomes appear in [69] while the major findings are repeated in Fig. 9.

Figure 8: Selected lattice-based PQC algorithms and the corresponding implementations utilized in this study. Red-colored text inside the parenthesis specifies selected security parameters.

To evaluate the area and power results in Fig. 9, I have added the area and power of

Figure 9: Total area and power of the studied NIST lattice-based PQC algorithms on 65nm process technology.

memory, multiplier, and hash operations together. The area for memory is investigated in terms of read-only (ROM) and read-access (RAM) memories. The instances of the required ROM and RAMs are generated using a commercial memory compiler from a partner foundry. For the corresponding PQC algorithm of Table 1, I have implemented Algorithms 1 to 4 for polynomials multiplication. The hash algorithms of column three of Table 1 are also implemented. For details about polynomials' input and output lengths, required memory sizes for ROM and RAM, and input and output of hash functions, readers can follow [69]. Consequently, the CRYSTALS-Kyber algorithm utilizes lower resources and consumes less power than other NIST round three candidates. On the other hand, the CRYSTALS-Dilithium takes higher resources but consumes lower power than the SABER algorithm, as shown in Fig. 9. Therefore, due to its simple mathematical structure, I selected SABER for further investigations in this thesis. Hence, the following text overviews SABER, including its building blocks.

## 2.3 SABER PQC KEM Protocol

SABER [21] provides security against Chosen-Ciphertext Attacks (IND-CCA), and its security hardness depends upon solving the module variant of the LWR problem (mod-LWR) [48]. A mod-LWR sample is defined by  $(a, b = \lfloor \frac{p}{q}(a^T s) \rceil) \in \mathcal{R}^{l \times 1} \times \mathcal{R}_p$ . Here, a denotes a vector of randomly generated polynomials in  $\mathcal{R}_q$ , s determines a secret vector of polynomials in  $\mathcal{R}_q$  whose polynomial coefficients are sampled from a binomial distribution, and the modulus p is less than q. The decisional variant of the problem is about finding a way to distinguish between two types of samples (mod-LWR and uniformly random) in  $\mathcal{R}_q^{l \times 1} \times \mathcal{R}_p$ . Moreover, SABER uses the Mod-LWR problem with p and q being power-of-two to construct a public-key encryption (PKE) scheme that is secure against Chosen Plaintext Attacks (IND-CPA). The PKE scheme supports the following cryptographic operations: (i) generation of a pair of public and private keys (PKE.KEYGEN), (ii) encryption (PKE.ENC), and (iii) decryption (PKE.DEC). The related algorithms to execute these operations are described in algorithms 5, 6, and 7. Similarly, for the KEM operations, the following are supported: (i) generation of a pair of public and private keys (KEM.KEYGEN), (ii) encapsulation (KEM.ENCAPS), and (iii) decapsulation (KEM.DECAPS). The algorithms for these operations are described in algorithms 8, 9, and 10.

#### Algorithm 5: SABER.PKE.KEYGEN() [30]

Input: SABER Parameter Lengths Output:  $pk \leftarrow (seed_A, b), sk \leftarrow (s)$  $seed_A \leftarrow \mathcal{U}(\{0,1\}^{256})$  $A \leftarrow gen(seed_A) \in \mathcal{R}_q^{l \times l}$  $r \leftarrow \mathcal{U}(\{0,1\}^{256})$  $s \leftarrow \beta_\mu(\mathcal{R}_q^{l \times l}; r)$  $b \leftarrow ((A^T s + h) \mod q) \gg (\epsilon_q - \epsilon_p) \in \mathcal{R}_p^{l \times l}$ 6 return  $pk \leftarrow (seed_A, b), sk \leftarrow (s)$

#### Algorithm 6: SABER.PKE.ENC() [30]

$\begin{array}{l} \text{Input: } pk \Leftarrow (seed_A, b), m \in R_2; r) \\ \text{Output: } c \Leftarrow (c_m, b') \\ 1 \ A \Leftarrow gen(seed_A) \in \mathcal{R}_q^{l \times l} \\ 2 \ \text{if } r \ is \ not \ specified \ \textbf{then}} \\ 3 \ \left\lfloor \ r \notin \mathcal{U}(\{0,1\}^{256}) \\ 4 \ s' \Leftarrow \beta_\mu(\mathcal{R}_q^{l \times l}; r) \\ 5 \ b' \Leftarrow ((As' + h) \ mod \ q) \gg (\epsilon_q - \epsilon_p) \in \mathcal{R}_p^{l \times 1} \\ 6 \ v' \Leftarrow b^T(s' \ mod \ p) \in R_p \\ 7 \ c_m \Leftarrow (v' + h_1 - 2^{\epsilon_p - 1}m \ mod \ p) \gg (\epsilon_p - \epsilon_T) \in \mathcal{R}_T \\ 8 \ \text{return} \ c \Leftarrow (c_m, b') \end{array}$

#### Algorithm 7: SABER.PKE.DEC() [30]

$\begin{array}{ll} \mbox{Input: } sk \Leftarrow s, c \Leftarrow (c_m, b') \\ \mbox{Output: } m' \\ \mbox{1 } v \Leftarrow b'^T (s \ mod \ p) \in \mathcal{R}_p \\ \mbox{2 } m' \Leftarrow ((v - 2^{\epsilon_p - \epsilon_T} c_m + h_2) \ mod \ p) \gg (\epsilon_p - 1) \in \mathcal{R}_2 \\ \mbox{3 } \mbox{return } c \Leftarrow (c_m, b') \end{array}$

#### Algorithm 8: SABER.KEM.KEYGEN() [30]

Input: SABER.PKE.KEYGEN() Output:  $pk \leftarrow (seed_A, b), sk \leftarrow (s, z, pkh)$ 1  $pk \leftarrow (seed_A, b)$ 2  $pkh \leftarrow \mathcal{F}(pk)$ 3  $z \leftarrow \mathcal{U}(\{0, 1\}^{256})$ 4 return  $pk \leftarrow (seed_A, b), sk \leftarrow (s, z, pkh)$

#### Algorithm 9: SABER.KEM.ENCAPS() [30]

Input:  $pk \leftarrow (seed_A, b)$ Output: c, K1  $m \leftarrow \mathcal{U}(\{0, 1\}^{256})$ 2  $(\hat{K}, r) \leftarrow \mathcal{G}(\mathcal{F}(pk), m)$ 3  $c \leftarrow \mathsf{SABER.PKE.ENC}(pk, m; r)$ 4  $K \leftarrow \mathcal{F}(\hat{K}, c)$ 5 return  $pk \leftarrow (seed_A, b), sk \leftarrow (s, z, pkh)$

Algorithm 10: SABER.KEM.DECAPS() [30]

Input:  $sk \leftarrow (s, z, pkh), pk \leftarrow (seed_A, b), c$ Output: K1  $m' \leftarrow SABER.PKE.DEC(s, c)$ 2  $(\hat{K}', r') \leftarrow \mathcal{G}(pkh, m')$ 3  $c' \leftarrow SABER.PKE.ENC(pk, m'; r')$ 4 if c = c' then 5  $\lfloor K \leftarrow \mathcal{H}(\hat{K}', c)$ 6 else 7  $\lfloor K \leftarrow \mathcal{H}(z, c)$ 8 return  $pk \leftarrow (seed_A, b), sk \leftarrow (s, z, pkh)$

In algorithms 5 to 10, the coefficients of the secret vectors s and s' are sampled from a centered binomial distribution  $\beta_{\mu}(\mathcal{R}_q^{l \times 1})$  with a parameter  $\mu$ , where  $\mu < p$ . The hash functions used in the SABER protocol are determined by  $\mathcal{F}$ ,  $\mathcal{G}$ , and  $\mathcal{H}$ .  $\mathcal{F}$  and  $\mathcal{H}$  are implemented using SHA3-256, while  $\mathcal{G}$  is implemented using SHA3-512. A variant of SABER,  $\mathcal{U}$ , samples the secret vectors s and s' from a centered uniform distribution instead of the binomial distribution. This makes the secret generation more efficient, as sampling from  $\mathcal{U}$  is simpler than sampling from  $\beta_{\mu}$ . The constant polynomials used in SABER are  $h_1$  and  $h_2$ . The implementation constants l,  $\epsilon_q$ ,  $\epsilon_p$ , and  $\epsilon_T$  have values of 3, 13, 10, and 4 for SABER. Different operations of SABER are further described in the following points.

- PKE.KEYGEN begins by randomly generating a seed that defines an l×l matrix A comprising l<sup>2</sup> polynomials in R<sub>q</sub>. A function gen of Algorithm 5 is used to generating a matrix from the seed based on SHAKE-128. A secret vector s of polynomials is also generated. These polynomials are sampled from a centered binomial distribution. The generated public key contains a matrix seed and rounded product A<sup>T</sup>s, while the secret key contains a secret vector s. KEM.KEYGEN follows the same steps as used for the PKE.KEYGEN, except that it appends a secret key with a hash of the public key and a randomly generated string z.

- The PKE.ENC operation consists of generating a new secret s' and adding a message to the inner product between the public key and the new secret s'. This forms the first part of the ciphertext while the second part contains the rounded product As'. The KEM.ENCAPS operation starts by randomly generating a message m and obtaining from that the public key. The ciphertext c contains the encrypted message and a value achieved from the message and public key.

- PKE.DEC requires the secret key s to extract the original message from the inner product between the public and secret keys. It is the counterpart to PKE.ENC. KEM.DECAPS re-encrypts the obtained message with the randomness associated with it and checks whether the ciphertext corresponds to the one received.

SABER offers three variants to target different security levels: LightSABER, SABER, and Fire SABER. The supported parameters to implement variants of SABER are given in Table 2. The values of the implementation constants used in algorithms 5 to 10 can be chosen from the SABER reference document [21]. Table 2 shows that, for the same

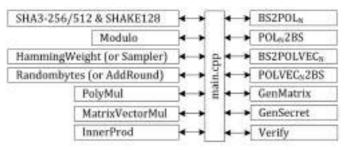

parameter size, three variants of SABER differ only in the secret key size. Moreover, the required building blocks are shown in Fig 10 to implement three variants of SABER.

SL; Public-key (B) Secret-key (B) Cipher-text (B) Light SABER (PKE & KEM):  $l = 2, n = 256, q = 2^{13}, p = 2^{10}, T = 2^3, \mu = 10$ 832 (for PKE) & 1568 (for KEM)  $SL_1$ 736 672 SABER (PKE & KEM): l = 3, n = 256,  $q = 2^{13}$ ,  $p = 2^{10}$ ,  $T = 2^4$ ,  $\mu = 8$ 1248 (for PKE) & 2304 (for KEM) 1088 SL<sub>3</sub> 992 Fire SABER (PKE & KEM): l = 4, n = 256,  $q = 2^{13}$ ,  $p = 2^{10}$ ,  $T = 2^6$ ,  $\mu = 6$ 1664 (for PKE) & 3040 (for KEM) SL<sub>5</sub> 1312 1472

Table 2: Security parameters of SABER for PKE and KEM operations (taken from [21])

$SL_i$ : Security levels,  $SL_1$ : equivalent to AES-128,  $SL_3$ : equivalent to AES-192  $SL_5$ : equivalent to AES-256.

(a) Concerning SABER specification document [21].

(b) Regarding FPGA-based hardware design of [30].

Figure 10: SABER building blocks.

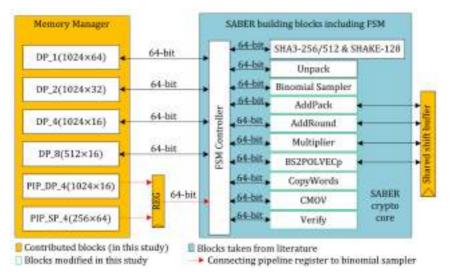

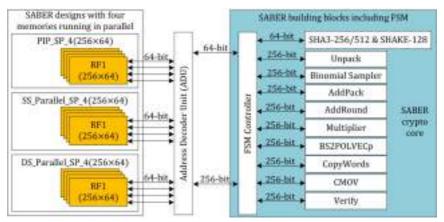

Fig. 10(a) provides the SABER building blocks concerning its specification document of [21], where all the blocks are implemented in C/C++ and called in a main file to execute the sequence of SABER operations. The building blocks, shown in Fig. 10(b), are regarding FPGA-based reference SABER implementation of [30], where blocks on

the left are the arithmetic and logical units and these blocks shares storage element amongst them to keep intermediate and the final results after the computations.

The blocks of Fig. 10(a) and Fig. 10(b) operate identically with some additional logic. For example, the SHA3-256/512 & SHAKE128 implemented as a wrapper to operate variants of SHA3, GenMatrix and GenSecret blocks of Fig. 10(b). Similarly, a polynomial multiplier is also implemented as a wrapper in Fig. 10(b), and it implements PolyMul, MatrixVectorMul, and InnerProd blocks of Fig. 10(a). The HammingWeight and Randombytes blocks of Fig. 10(a) correspond to the sampler and AddRound blocks of Fig. 10(b). Moreover, the BS2POL<sub>N</sub> and POL<sub>N</sub>2BS blocks of Fig. 10(a) correspond to Unpack and AddPack units. The additional CMOV and CopyWords blocks in Fig. 10(b) need to compute matrix transpose by shifting rows with the columns and vice versa. In short, the strategies to implement these building blocks are described in the text below.

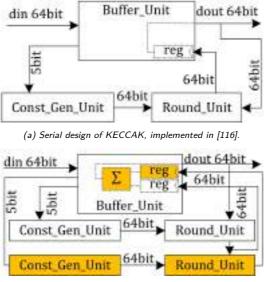

SABER requires several hash functions such as variants of SHA3 (256/512) and an extended output function, i.e., SHAKE128, for different purposes such as binomial sampling. All these functions are standardized in FIPS-202 [68]. SHA3-256 takes the input byte string from the byte array of length l and generates the output byte string of length 32. Similarly, SHA3-512 takes the input byte string from the byte array of length l and generates the output byte string of length 64. SHAKE128 receives the input byte string from the byte array of length l and generates the output byte string of length L. The execution of all these hash functions is based on a KECCAK sponge function [68] to compute the permutations. The building blocks of KECCAK are *theta*, *pi*, *rho*, *chi*, and *iota*. To understand KECCAK building blocks, interested readers are referred to follow the KECCAK specification document [68].

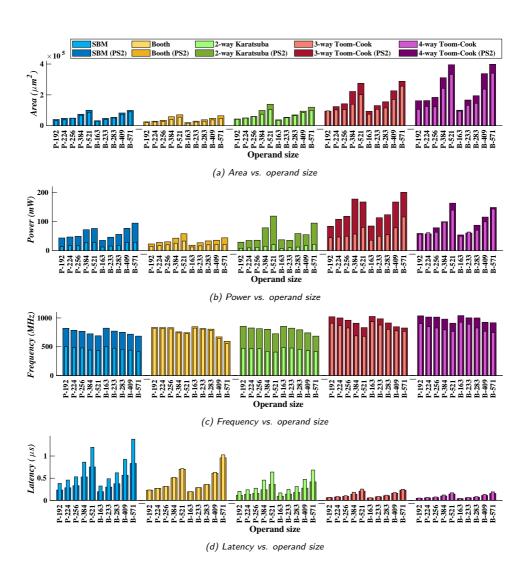

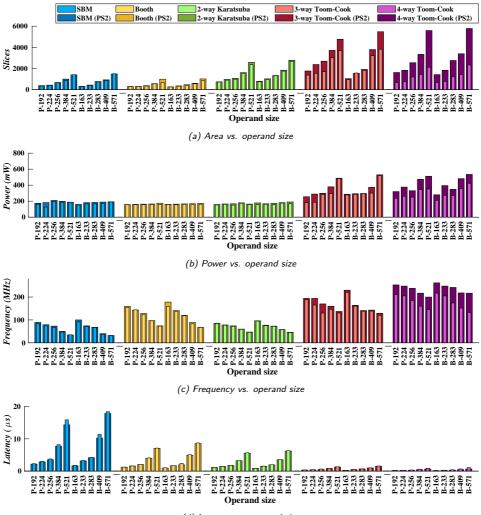

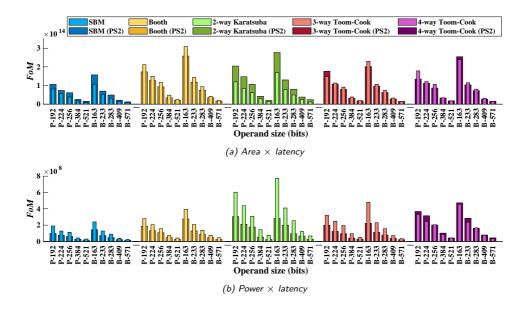

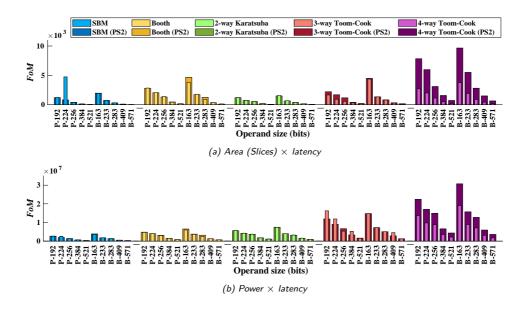

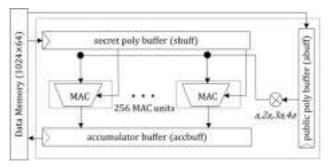

SABER involves polynomial-to-polynomial multiplications and matrix-to-vector multiplication. In polynomial-to-polynomial multiplications, the corresponding inputs and produced output are in polynomials. In matrix-to-vector multiplication, the first input to the multiplier is a matrix that belongs to  $R_q^{l \times 1}$  while the second input is a vector v, and it returns the products in a vector. Several approaches exist in the literature to operate these (polynomial-to-polynomial and matrix-to-vector) multiplications. These approaches include schoolbook [70, 71], Karatsuba [69, 72, 73], Toom-Cook [74, 75], NTT [65], Booth [62], etc. Since SABER uses a power-of-two moduli  $p = 2^{10}$  and  $q = 2^{13}$  [30]; therefore NTT-based multiplication could be applied but has no benefit and even, it worse the performance of the SABER [76] – while the remaining methods can be applied to perform polynomial coefficient multiplications. The mathematical structures of these polynomial multiplication methods are already described in Section 2.2.