Test Lab (Optional)

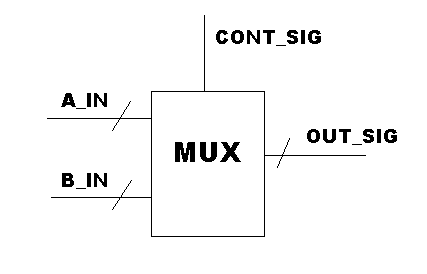

Mux.vhd file is the design file of a multiplexer, which its behavior is presented in Table 1. If the control signal CONT_SIG is '1' , then the input A_IN is propagated to the output OUT_SIG, otherwise, if the CONT_SIG is '0' , then input B_IN is propagated to the output.

Table 1: Behaviour of Mux.vhd

| CONT_SIG value | OUT_SIG value |

| 1 | A_IN |

| 0 | B_IN |

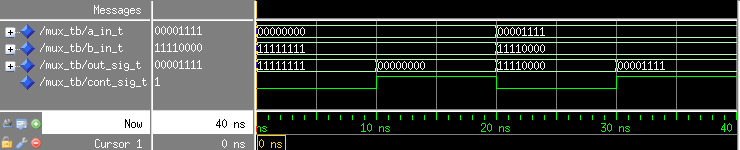

Figure 2. Simulation example

Tasks

- Take the guide for ModelSim simulator and try to compile first design file mux.vhd. Also take the testbench file mux_tb.vhd. Simulate the design and check the behavior.

- Design mux.vhd contains errors. Fix the errors and make sure that the behavior of the design is correct.

- Repeat the simulations using: Xilinx ISE guide.

- Change the code so that instead of sensitivity list the process uses wait command. Make sure the code is correct by simulation. Choose a simulator you like best (ISE or ModelSim).

- Answer the questions.

Questions

- Explain the errors.

- What is the difference of entity and architecture?

- Can one entity have more than one architecture? Explain.

- Is it possible to get right waveforms of the signals during the simulation, even when your design contains behavioral errors? Give an example based on the lab.

Related Readings