Finite State Machine (FSM)

Task description

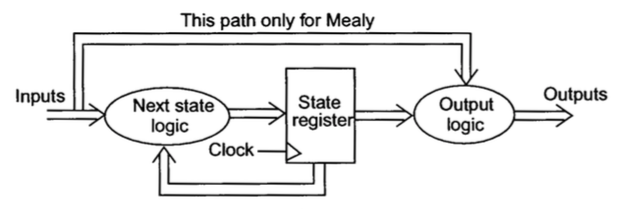

A Finite State Machine (FSM) has two major forms:

- Moore machine: in this type of FSM the output of the circuit is dependent only on the state of the machine and not on its inputs.

- Mealy machine: in this type of FSM the output of the circuit is dependent both on themachine state and also its inputs.

Figure 1. A Finite State Machine (FSM) (Moore and Mealy)

Each of the blocks shown in Figure can be modelled using a process. Since the details FSMs in general is provided in the same tutorial in VHDL, it is not mentioned here. The goal of this tutorial is to describe the same FSMs in the VHDL tutorial in SystemC.

Tasks

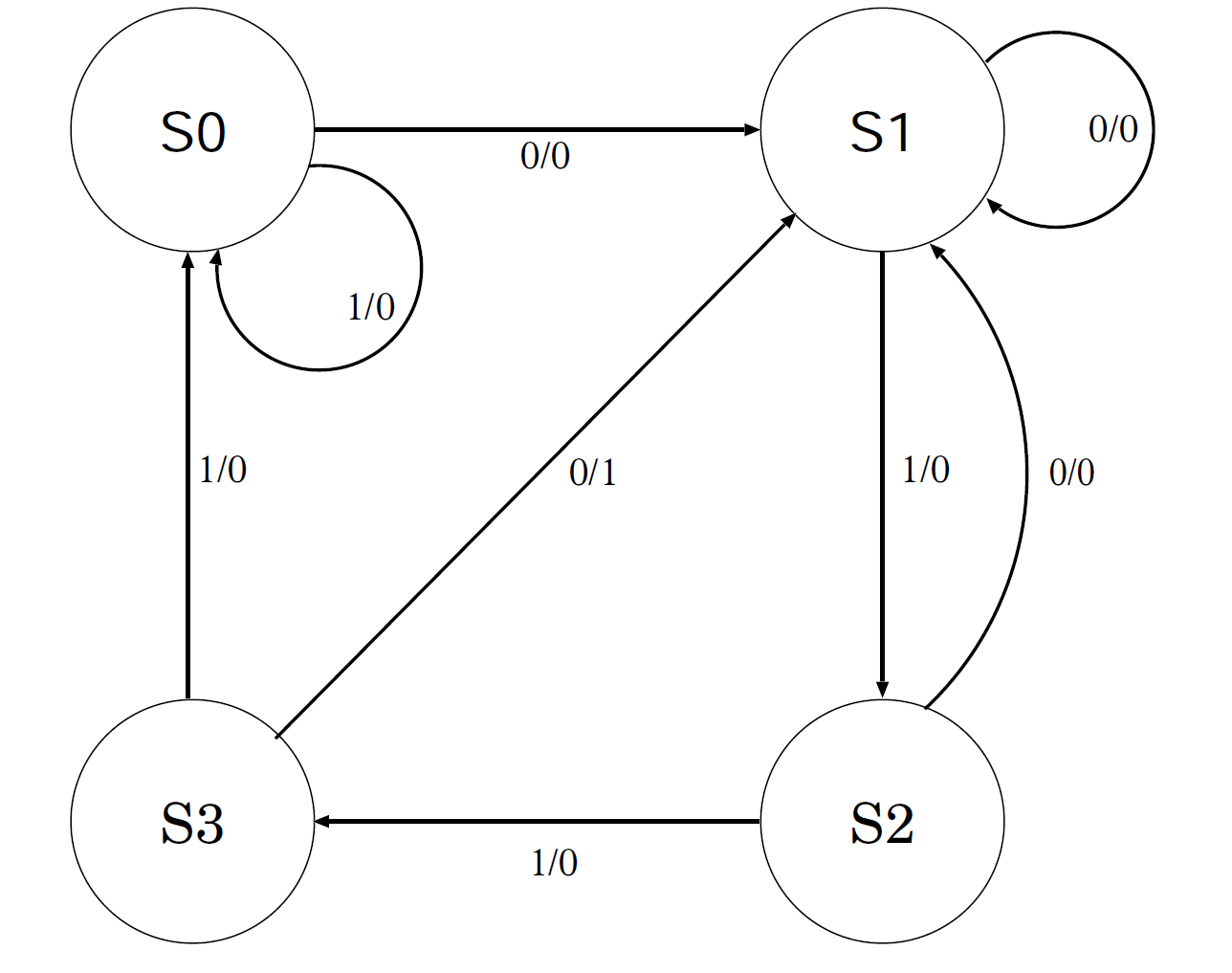

- Consider the FSM shown in Figure 2 (which is the same as the one used in the VHDL FSM tutorial). This is a mealy state machine, which takes one input and looks for the pattern “0110”. Whenever the pattern is found, the output goes 1. You should already have the tables for the FSM, State Transition Table and Output Function Table.

Figure 2. A Mealy FSM (used in VHDL tutorial)

- Since first we want to design a mealy FSM, we provide a sample as a template. Try to study the sample FSM FSM.h and FSM.cpp files along with the test-bench provided FSM_tb.cpp. Simulate and visualize the results using GTKWave.

- Now, Try to re-design the FSM you designed in the VHDL tutorial, shown in Figure 2. Use the previous sample FSM files as your template. Name your design files mealy_fsm.h and mealy_fsm.cpp.

- Write a test-bench in SystemC, using the previous fsm_tb.cpp as template, which generates a test pattern of 0,1,1,0,1,1,0,0,1,1,0,1,1,1,1,1.

- Now change the design to a Moore FSM. Try to re-write the Moore FSM you designed in the VHDL tutorial for FSMs in SystemC. Re-use the test-bench with the same test pattern and make sure the design still works properly.

Related Readings