- AND Gate

Inputs Outputs In1 In2 Out 0 0 0 0 1 X 1 0 X 1 1 1 - OR Gate

Inputs Outputs In1 In2 Out 0 0 0 0 1 X 1 0 X 1 1 1 - XOR Gate

Inputs Outputs In1 In2 Out 0 0 0 0 1 X 1 0 X 1 1 X - NAND Gate

Inputs Outputs In1 In2 Out 0 0 1 0 1 X 1 0 X 1 1 0 - NOR Gate

Inputs Outputs In1 In2 Out 0 0 1 0 1 X 1 0 X 1 1 0 - NOT Gate

Inputs Outputs In Out 0 X 1 X - Given the following truth table make Karnaugh map (K-Map) of the following design

Inputs Outputs X Y Or A 0 0 0 0 0 1 0 1 1 0 0 1 1 1 1 1 - Based on the K-Map write the minimized boolean equation

- Write the boolean equation for half adder

- Write the boolean equation for full adder

- Make a schematic diagram for a daisy chain adder using full adders and half adders? Illustrate by making a diagram.

- How do we convert a full daisy chain adder into an adder subtracter? Illustrate by making a schematic diagram using full adder and any logical gate necessary.

- Illustrate the critical path of a daisy chain adder.

- Illustrate the critical path of a daisy chain subtracter.

- Considering the following operators write the boolean equation from task 1.h in VHDL syntax. (consider all inputs and outputs as signals) (HINT: LOOK AT THE EXAMPLE)

VHDL OPERATOR USE Example AND logical and infix operator which is used with logical array or boolean type of signals or variables. in1 and in2 OR logical or infix operator which is used with logical array or boolean type of signals or variables. in1 or in2 NAND logical nand infix operator which is used with logical array or boolean type of signals or variables. in1 nand in2 NOR logical nor infix operator which is used with logical array or boolean type of signals or variables. in1 nor in2 XOR logical exclusive or infix operator which is used with logical array or boolean type of signals or variables. in1 xor in2 XNOR logical exclusive nor infix operator which is used with logical array or boolean type of signals or variables. in1 xnor in2 NOT logical or prefix operator which is used with logical array or boolean type of signals or variables. not in <= Assignment operator which assigns the right hand side signal or variable to the left hand side signals. out <= in; := Assignment operator which assigns the right hand side signal or variable to the left hand side variable. out := in; - If all right hand side is replaced with a signal what changes will take place in the previous equation in 2a? (HINT: READ THE VHDL OPERATOR TABLE in 2a)

- If all left hand side is replaced with a signal what changes will take place in the previous equation in 2a? (HINT: READ THE VHDL OPERATOR TABLE in 2a)

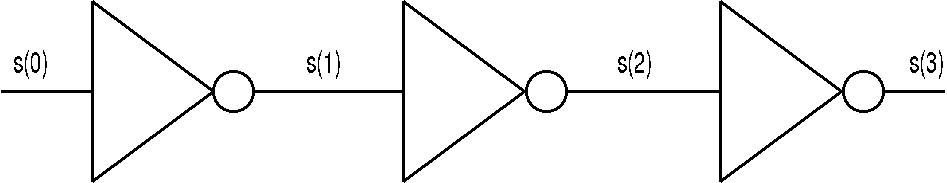

- Consider a four bit signal s . Write the syntax for instantiation of following entity with signal s using a generate statement according to the following figure.

entity my_not_gate is

port (

input : in std_logic;

output : out std_logic

);

end my_not_gate;