PicoCPU

The picoCPU was built as a course work during the Digital Systems Modelling and Synthesis course. Its goal is to provide very simple and minimal, but still functional, general purpose CPU design for educational purposes.

Contents

Architecture

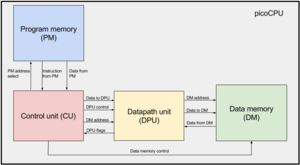

PicoCPU is divided into four main components (seen in the figure on the right):

- Control Unit (CU): Reads the instructions, advances the program counter and controls the work of the rest of the CPU

- Data Path Unit (DPU): Does all the calculations and other data manipulation operations

- Instruction Memory (IM): A ROM that contains the program data. In picoCPU, it is emulated by the testbench.

- Data memory (DM): The data memory is implemented as a RAM. It contains the temporary data that are needed by the currently running program.

PicoCPU is designed to have a generic design and it's bitwidth is scalable to satisfy the user's preference, being 8-bit by default. All the data are always treated as signed values.

Control Unit

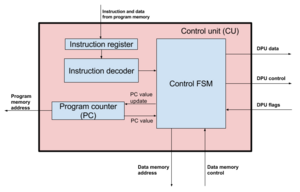

The most important part of the CU is the control FSM, that has four states:

- Fetch: fetches the data from the instruction memory and stores it in the instruction register.

- Decode: Seperates operand from instruction

- Execute: Executes the instruction

- Write back: Writes execution result to the destination register or memory address, advances the program counter.

The program counter (PC) is a pointer to the instruction memory address of the currently executed instruction. The program counter's value directly specifies the memory address for reading the instruction memory. Usually, the program counter is increased by one after the current instruction is loaded (next address of the instruction memory is chosen). However, it is also possible to change the PC's value to an arbitrary one, for example to implement branching in the code.

Data Path Unit

ALU

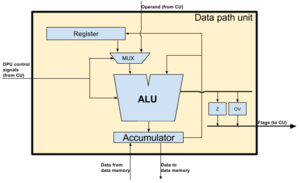

The central part of the DPU is the Arithmetic and Logic Unit (ALU). ALU's task is to execute all the arithmetical and logical calculations. It has many functions and the correct one is chosen by the CU, based on the currently executed instruction. Every calculation result always ends up in the accumulator register. The first input of the ALU can be multiplexed between a register and the operand from the operand from the instruction memory and the contents of a register (the multiplexor can be controlled be specific instructions). The second input is always the contents of the accumulator.

Memory operations

Writing to and reading from the data memory always involves the accumulator - all data read from the memory always ends up in the accumulator. It is also only possible to write into the memory data that is stored in the accumulator.

For writing into the register, the file data to be written has to be already in the accumulator. Then, a special instruction is used for doing the writing. Reading from the register can be done only through the ALU, using the regular ALU-related instructions, just the MUX has to be configured to take its input from the register. Due to the fact that it is possible to access the register only through the ALU, the value of the register can only be retrieved by running an arithmetic or logic operation on it. If just retreaving of the value is desired, a neutral operation, that does not change the value can be performed, like adding or subtracting 0 to/from the register or AND-ing the value with 1-s.

Flags

The picoCPU features two flags: zero (Z) and overflow(OV)

The zero flag indicates that the value in the accumulator is equal to 0 and OV flag indicates that the last operation caused an overflow in the accumulator. User can access the values of these flags using some conditional branching functions (BranchIfZero, etc.). The flags are only held up as long as the condition for a flag is true (i.e. the accumulator is zero) and are, thus, usually available only to the next isntruction (except some neutral instructions like NOP, that are not data-related).